**EAE SIE 2**

#### **SESSION 2020**

# AGREGATION CONCOURS EXTERNE

Section: SCIENCES INDUSTRIELLES DE L'INGÉNIEUR

Option : SCIENCES INDUSTRIELLES DE L'INGÉNIEUR ET INGÉNIERIE ÉLECTRIQUE

# MODÉLISATION D'UN SYSTÈME, D'UN PROCÉDÉ OU D'UNE ORGANISATION

Durée: 6 heures

Calculatrice électronique de poche - y compris calculatrice programmable, alphanumérique ou à écran graphique – à fonctionnement autonome, non imprimante, autorisée conformément à la circulaire n° 99-186 du 16 novembre 1999.

L'usage de tout ouvrage de référence, de tout dictionnaire et de tout autre matériel électronique est rigoureusement interdit.

Si vous repérez ce qui vous semble être une erreur d'énoncé, vous devez le signaler très lisiblement sur votre copie, en proposer la correction et poursuivre l'épreuve en conséquence. De même, si cela vous conduit à formuler une ou plusieurs hypothèses, vous devez la (ou les) mentionner explicitement.

NB: Conformément au principe d'anonymat, votre copie ne doit comporter aucun signe distinctif, tel que nom, signature, origine, etc. Si le travail qui vous est demandé consiste notamment en la rédaction d'un projet ou d'une note, vous devrez impérativement vous abstenir de la signer ou de l'identifier.

# **INFORMATION AUX CANDIDATS**

Vous trouverez ci-après les codes nécessaires vous permettant de compléter les rubriques figurant en en-tête de votre copie.

Ces codes doivent être reportés sur chacune des copies que vous remettrez.

#### ROBOT MOBILE UNICYCLE

# Ce sujet comporte:

Le texte du sujet Pages DQ1 à DQ34 Les documents réponses Pages DR1 à DR10 Les documents ressources annexes Pages A1 à A53

# Ce sujet comporte 8 parties indépendantes :

- Partie A Génération des horloges de fonctionnement.

- Partie B Analyse de la communication inter-cartes dans le robot.

- Partie C Asservissement du robot.

- Partie D Analyse de la partie variation de vitesse du robot.

- Partie E Analyse des accéléromètres.

- Partie F Analyse de la fonction élévatrice de tension.

- Partie G Analyse de la fonction odométrie.

- Partie H Analyse d'un code programmé.

# Une lecture préalable et complète du sujet est indispensable.

Il sera tenu compte de la cohérence avec laquelle les candidats traiteront chaque partie, le jury préférant une réflexion d'ensemble de la partie abordée à un éparpillement des réponses.

Chaque question est repérée par un numéro. Les candidats sont invités à numéroter chaque page de leur copie et à indiquer clairement le numéro de la question traitée. Les candidats sont priés de rédiger chacune des huit différentes parties du problème sur feuilles séparées et clairement repérées.

Il leur est rappelé qu'ils doivent utiliser les notations propres au sujet, présenter clairement les calculs et dégager ou encadrer tous les résultats.

Tout résultat incorrectement exprimé ne sera pas pris en compte. En outre les correcteurs leur sauront gré d'écrire lisiblement et de soigner la qualité de leur copie. Il sera tenu compte de la qualité de rédaction, en particulier pour les réponses aux questions ne nécessitant pas de calcul. Le correcteur attend des phrases complètes respectant la syntaxe de la langue française.

Pour la présentation des applications numériques, il est rappelé que lors du passage d'une forme littérale à son application numérique, il est recommandé aux candidats de procéder comme suit : après avoir rappelé la relation littérale, chaque grandeur est remplacée par sa valeur numérique en respectant la position qu'elle avait dans la relation puis le résultat numérique est donné sans calculs intermédiaires et sans omettre son unité.

Si le texte du sujet, ses questions ou ses annexes vous conduisent à formuler une ou plusieurs hypothèses, il vous est demandé de la (ou les) mentionner explicitement dans votre copie.

# 1 PRÉSENTATION DU SYSTÈME

# 1.1 PRÉSENTATION GÉNÉRALE

Le robot dont l'étude est proposée ici, est une version réduite d'une structure industrielle de type AGV (Automated Guided Vehicle), qui fonctionne sous l'environnement robotique ROS (Robot Operating System). Elle a été développée pour tester certains organes ainsi que l'environnement robotique et certaines fonctions de discussion. Elle est utilisée dans le cadre de tests d'asservissement et de communication des systèmes, et dans le cadre de la perception environnementale du robot.

Figure 1

Le robot, présenté en figure 1, a été conçu pour :

- être capable de se déplacer, à moyenne et grande vitesse,

- se repérer dans son environnement.

- être capable d'effectuer quelques actions simples,

- être autonome,

- communiquer avec l'extérieur (transmission d'informations ou guidage),

- accueillir l'environnement robotique ROS.

Seules les études de quelques fonctions du robot sont envisagées. Elles porteront sur des aspects électronique (oscillateur à quartz), informatique industrielle (configuration de microcontrôleur, communication, programmation), automatique (asservissement analogique et numérique), mécanique (odométrie, positionnement), et électronique de puissance (hacheur, élévateur de tension).

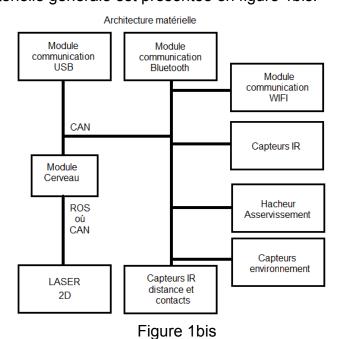

#### 1.2 PRÉSENTATION DU MATÉRIEL

Le robot est capable de communiquer avec l'extérieur, soit en WIFI, soit en Bluetooth, soit directement connecté par liaison USB avec un PC (utilisation en mode de recherche d'erreurs).

Comme l'étude ne porte que sur le robot lui-même, le pilotage et la récupération des données sur PC ou tablette ne seront pas présentés.

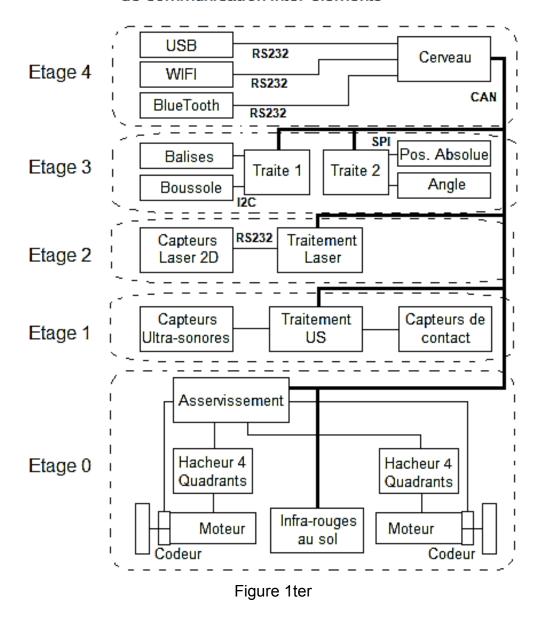

L'architecture du robot est composée de 5 étages distincts (voir figure 1) assurant chacun une fonction particulière.

Les étages et les fonctions des divers étages du robot sont donnés ci-dessous.

- Etage 0 : capteur IR au sol, alimentation et pilotage des moteurs à courant continu.

- Cet étage permet au robot de se déplacer et de repérer des indications au sol. C'est sur cet étage que l'on retrouve les 2 batteries utilisées pour fournir l'énergie.

- Etage 1 : capteur de distance à Ultrasons et capteur de contact.

Cet étage retourne au robot des informations de distance par rapport aux éléments de son environnement (mesure Ultrasonore) et fournit des indications en cas de choc.

- Etage 2 : capteur d'environnement Laser 2D.

Cet étage retourne au robot d'autres informations de distance par rapport aux éléments de son environnement. Elles sont basées sur une mesure Laser. Ce Laser 2D est compatible ROS.

- Etage 3 : détection positionnement balise IR, boussole, positionnement absolu et angle du robot.

Grace à cet étage, le robot a une connaissance de son positionnement absolu

- sur un terrain.

- Etage 4 : Cerveau, communication (WIFI, Bluetooth, USB).

Cet étage est utilisé pour le pilotage du robot, soit par la carte cerveau (exécution des stratégies de fonctionnement), soit par des commandes externes.

L'architecture matérielle générale est présentée en figure 1bis.

L'architecture matérielle du robot est composée majoritairement de cartes de traitement d'informations issues des capteurs, d'une carte de commande de moteurs à courant continu, ainsi que de modules de communication. La discussion interne au robot s'effectue à travers un bus de communication qui exploite le protocole CAN. Certains capteurs, comme le capteur Laser, sont prévus pour s'adapter au système d'exploitation robotique ROS.

La figure 1ter représente une description par étages du robot qui intègre tous les protocoles utilisés lors des diverses discussions inter-cartes.

# Architecture suivant les étages avec intégration des protocoles de communication inter-éléments

Tous ces étages communiquent ensemble à travers un bus CAN.

Le bus CAN est un bus série multiplexé permettant à différents éléments de s'échanger des informations au sein de trames CAN. Ces dernières comportent les

données utiles à transmettre ainsi que, entre autres, l'adresse et l'identifiant du composant émetteur.

Les données utiles sont de longueur variable suivant l'étage.

Pour la communication CAN, le tableau récapitulatif suivant présente les différentes adresses et identifiants (ID) de chaque carte.

| Etage                            | Adresse | Identifiant |

|----------------------------------|---------|-------------|

| Etage 0 : IR au sol              | 0x07A3  | 3           |

| Commande des Moteurs             | 0x07A1  | 1           |

| Etage 1 : Capteurs US et contact | 0x07A2  | 2           |

| Etage 2 : Laser 2D               | 0x07A4  | 4           |

| Etage 3 : Balise, boussole       | 0x07A5  | 5           |

| Positionnement, angle            | 0x07A6  | 6           |

| Etage 4 : Cerveau                | 0x07A0  | 0           |

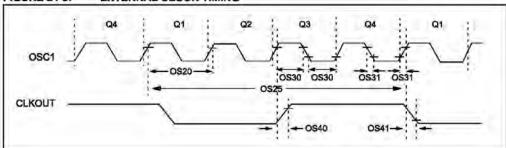

# Partie A: génération des horloges de fonctionnement

Introduction : les cartes électroniques de chacun des étages intègrent un microcontrôleur. Le temps de cycle des microcontrôleurs doit être assez précis car il est utilisé pour le cadencement du fonctionnement, pour effectuer des mesures et pour rythmer les communications. Il est basé sur l'utilisation d'un quartz.

# Le quartz -Modélisation.

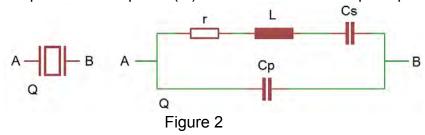

La figure 2 représente un quartz (Q) et son schéma électrique équivalent.

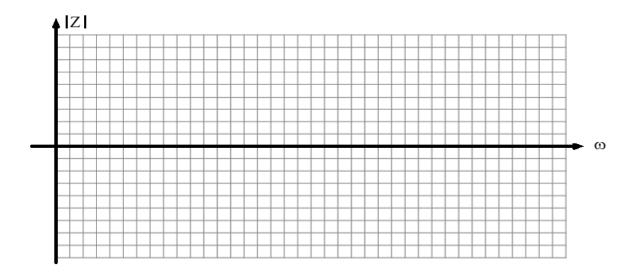

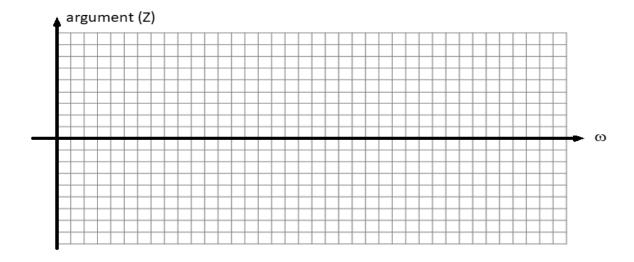

Question A-1 : calculer l'impédance complexe du quartz entre les points A et B (figure 2) et la mettre sous la forme suivante :  $Z(j\omega) = \frac{a+jb}{c+jd}$ Exprimer les grandeurs a, b, c et d en fonction de r, L, Cs, Cp et  $\omega$ .

Question A-2 : on néglige les pertes mécaniques du quartz. Proposer une écriture simplifiée de  $Z(j\omega)$ . Montrer que l'on peut écrire  $Z(j\omega) = j.X(\omega)$  et exprimer  $X(\omega)$  en fonction de L, Cs, Cp et  $\omega$ .

Exprimer ensuite  $\omega s$  et  $\omega p$ , correspondant respectivement aux pulsations qui annulent le numérateur et le dénominateur de  $Z(j\omega)$ . Puis, exprimer  $\omega p$  en fonction de  $\omega s$ , Cs et Cp.

Le quartz utilisé est un IQD modèle HC49/4H (documentation fournie en annexe 1). On considèrera que Cp = 40 fF, Cs = 6 pF, L = 398  $\mu$ H et r = 5  $\Omega$ .

Question A-3 : justifier et tracer sur le document réponse DR1, le module et l'argument de  $Z(j\omega)$ . Préciser, sur le document, en fonction de la fréquence, par quel type de dipôle simple le quartz peut être modélisé.

Préciser, de plus, la bande de fréquence à l'intérieur de laquelle le quartz peut être utilisé pour réaliser un oscillateur. Justifier la réponse.

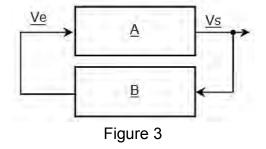

# Principe d'un oscillateur

Le principe d'un oscillateur est présenté en figure 3.

Question A-4: établir, à partir de la figure 3, les équations permettant de déterminer les conditions d'oscillation dites de Barkhausen. Indiquer la relation entre  $\underline{A}$  et  $\underline{B}$  pour que le système réalise un oscillateur, et en déduire, dans ces conditions, la relation liant  $|\underline{A}|$  et  $|\underline{B}|$  ainsi que la relation liant  $Arg[\underline{A}]$  et  $Arg[\underline{B}]$ .

Préciser la façon dont on peut s'assurer que la condition limite est atteinte.

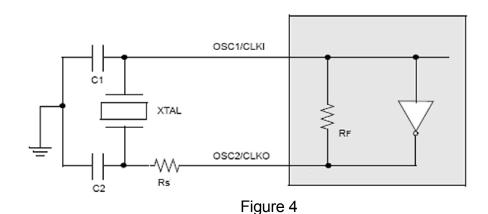

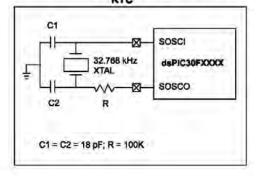

# Oscillateur à quartz d'une des cartes du robot

Dans la documentation constructeur du dsPIC33F, on donne le schéma utilisé pour réaliser l'oscillateur à quartz d'une des cartes à microcontrôleur du robot.

Une version simplifiée est présentée ci-après en figure 4 :

Dans le microcontrôleur, un inverseur logique est utilisé comme amplificateur. On considèrera, si nécessaire, que sa résistance d'entrée est infinie et que sa résistance de sortie est nulle.

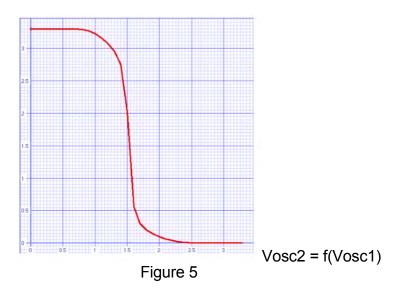

On a relevé sa caractéristique de transfert (figure 5) :

Question A-5 : indiquer lorsque l'inverseur logique est connecté conformément au schéma de la figure 4, son point de fonctionnement.

En déduire la valeur de son amplification que l'on notera A.

Question A-6 : en considérant RF infinie, calculer la fonction de transfert  $\underline{T} = \frac{\underline{Vosc1}}{\underline{Vosc2}}$  du réseau constitué par C1, C2, Rs et le quartz (on supposera que l'impédance du quartz est égale à j. $X(\omega)$ ).

Enoncer alors la condition pour que les oscillations existent.

Question A-7 : on a montré précédemment à la question A-3, que le quartz avait un comportement différent suivant sa fréquence de travail. Indiquer alors quelle doitêtre la nature du comportement du quartz pour que le système oscille. Calculer ensuite sa fréquence d'oscillation.

# Boucle à verrouillage de phase

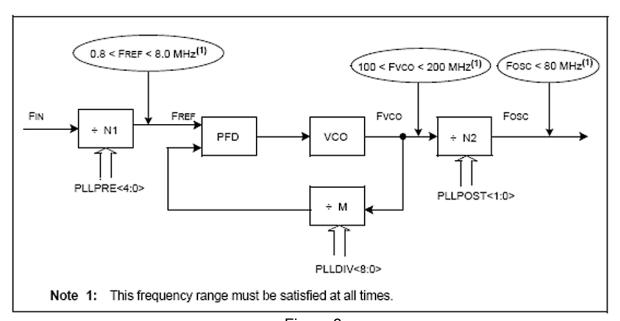

Pour augmenter la fréquence d'oscillation, un synthétiseur de fréquence est intégré à certains microcontrôleurs comme le montre la figure suivante (figure 6) :

Figure 6

On suppose que la boucle est verrouillée. La documentation fournie en annexe 2 donne les valeurs possibles de réglage pour N1, M et N2.

Question A-8 : exprimer la relation liant  $F_{REF}$  à  $F_{VCO}$ . En déduire la relation qui lie Fosc avec Fin, N1, M et N2.

Préciser les conditions pour que le pas de réglage de la fréquence F<sub>OSC</sub> soit minimal.

Application numérique : l'oscillateur primaire fonctionne à 4 MHz. On désire une fréquence d'oscillation de 40 MHz. On souhaite un pas de réglage de 0,25 MHz pour la fréquence d'oscillation. Calculer les valeurs des paramètres N1, M et N2 (on choisira la valeur maximale possible pour le taux de pré division N1).

Question A-9 : représenter, en suivant les consignes données ci-après, le contenu des 8 bits de poids faible des registres FOSC, FOSCSEL, CLKDIV et PLLFBD pour obtenir le fonctionnement précédent. Exprimer alors le contenu des 8 bits de poids faible de ces registres en hexadécimal.

On respectera pour remplir les différents bits des registres, les règles :

-- pour les bits inutilisés,

X pour les bits dont la valeur n'est pas importante,

0 ou 1 suivant l'état pour ceux qui sont importants.

Pour définir la valeur hexadécimale, on choisira la valeur 0 logique pour les bits inutilisés et pour les bits dont la valeur n'est pas importante, sauf si un commentaire explicite est fait dans la documentation.

# Partie B: analyse de la communication inter-cartes dans le robot – Protocole CAN

Introduction : les cartes électroniques de chacun des étages communiquent entre elles. Chacun des microcontrôleurs est équipé d'une interface matérielle CAN couplée à un émetteur-récepteur CAN haute vitesse.

#### Bits dominants - récessifs

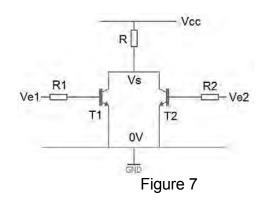

Question B-1 : à partir du schéma suivant (figure 7) :

Donner la table de vérité de la sortie Vs en fonction des entrées Ve1 et Ve2 pour la fonction ci-dessus et indiquer la fonction logique réalisée.

Préciser, par rapport aux entrées Ve1 et Ve2, quel est le niveau logique prioritaire.

Expliquer alors la notion de bits dominants et récessifs.

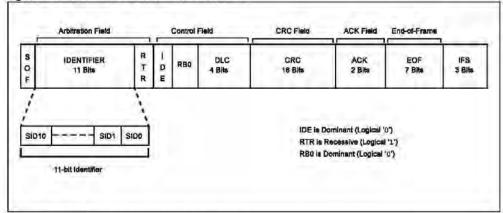

Question B-2 : le CAN du robot fonctionne en mode Standard (et non en mode étendu). L'annexe 3 présente le fonctionnement du bus CAN. Pour le CAN standard, préciser la taille des identificateurs, le nombre d'identificateurs possibles utilisables ainsi que le nombre de données maximum qui peuvent être transmises.

Indiquer alors, en nombre de bits, les longueurs minimales et maximales des trames de données (on ne prendra pas en compte les bits rajoutés automatiquement au message, et l'on supposera que l'on transmet au minimum une donnée).

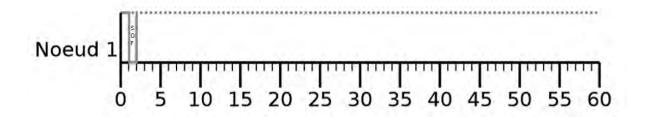

Le robot est composé de 7 nœuds (cerveau, moteur, US, IR, Laser, Balise, Positionnement) qui transmettent périodiquement des données avec le même débit de bus de 250 kbits/s. On supposera qu'une trame transmise quelconque est composée, en moyenne, de 2 octets d'informations utiles.

Question B-3 : pour chaque nœud, une trame est émise toute les 40 ms. Préciser tout d'abord combien de trames par secondes, au maximum, peuvent être transmises sur ce bus. Caractériser ensuite la charge réelle du bus CAN du robot.

Lorsqu'on transmet sur le bus, 5 fois d'affilée, le même bit, on insère un bit supplémentaire de polarité inverse : ce bit supplémentaire s'appelle bit de « stuffing ».

Question B-4 : sur le document réponse DR1, compléter le chronogramme de la transmission d'une donnée du cerveau (identifiant 0x7A0) suivi de 1 octet de valeur 0x80 puis du CRC de valeur 0x2EDC en tenant compte du phénomène du « Bit Stuffing ». On considèrera que la valeur des bits réservés du champ de contrôle est 0 et que le début de la transmission est matérialisé par le front descendant.

Pour le tracé, une graduation correspondra à un bit. Le CRC est un mot sur 15 bits suivi d'un délimiteur,1 bit, au niveau logique « 1 ». Le champ d'acquittement est codé sur 2 bits, le premier au niveau logique « 0 » suivi d'un deuxième au niveau logique « 1 ».

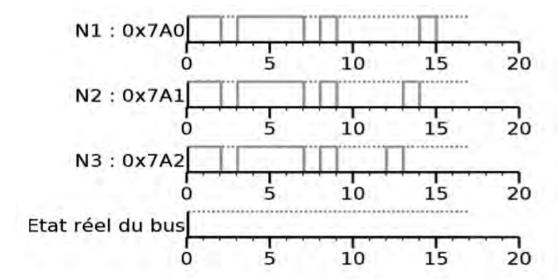

Chaque nœud peut émettre à tout moment. Des collisions peuvent donc avoir lieu. Le gestionnaire du bus CAN intègre un processus d'arbitrage. Il est basé sur le fait que, si deux ou plusieurs nœuds émettent en même temps, en comparant bit après bit, le premier qui aura un bit récessif face à un dominant perdra le bus. La procédure sera appliquée jusqu'à ce qu'il n'en reste plus qu'un.

Question B-5 : sur le document réponse DR2, compléter le chronogramme d'un arbitrage de transmission simultanée d'une donnée cerveau, moteur et capteur US. Au vu du choix des adresses dans le robot, expliquer comment est établie la priorité de la transmission.

Question B-6 : l'annexe 4 illustre le principe de calcul du CRC. Montrer que le CRC de la question B-4 vaut bien 0x2EDC.

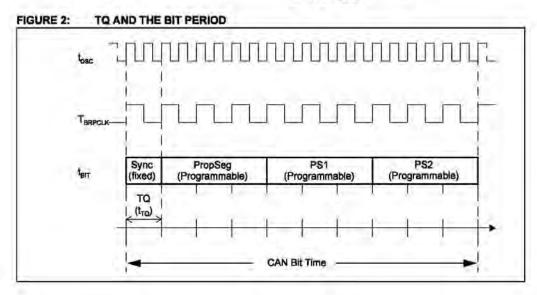

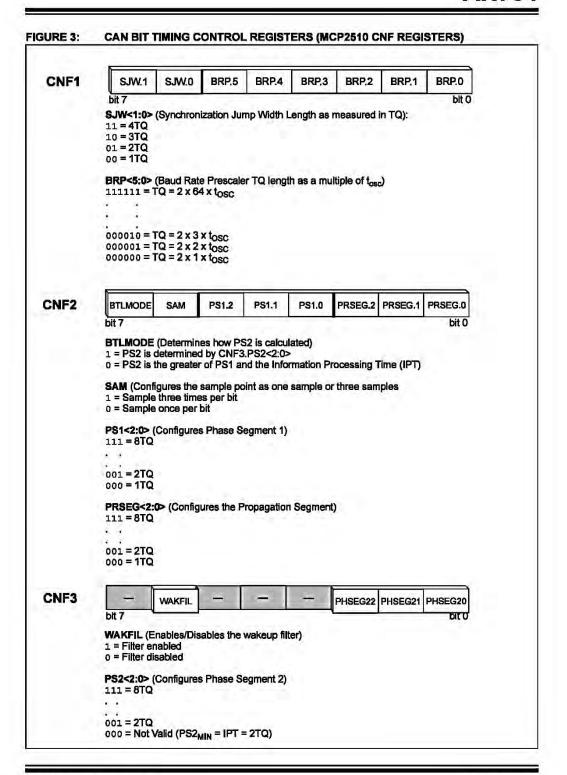

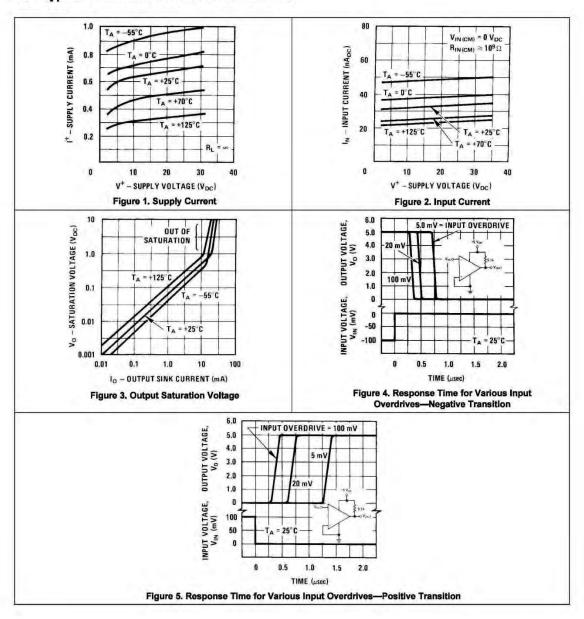

Les paramètres suivants ont été choisis : l'horloge CAN fonctionne à 40 MHz, la vitesse est de 250 kbits/s. On partage un bit en 8 parties (« time quantum ») et on lira et on interprètera la valeur du bit au bout de 75% de la durée du bit.

Question B-7 : valider, à l'aide de la documentation du microcontrôleur en annexes 5 et 6, que la valeur du registre C1CFG2, caractéristique du fonctionnement du CAN, est égale à 0x0199.

#### Partie C: asservissement du robot

Introduction : dans une première version, un asservissement de vitesse sur chacune des roues a été réalisé à l'aide d'un microcontrôleur.

Pour calculer le correcteur que l'on va implanter et qui servira au pilotage des machines à courant continu, on a effectué une identification de l'ensemble hacheur 4 quadrants, moteur à courant continu et capteur (tachymètre). L'étude sera menée comme si le fonctionnement était analogique, bien que la version finale implantée soit numérique.

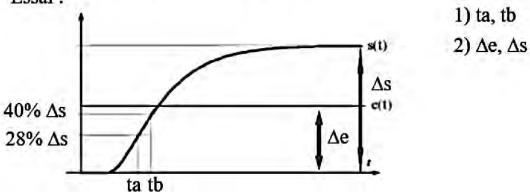

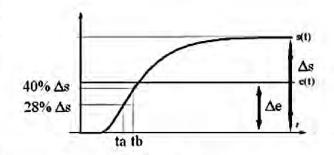

#### Identification en boucle ouverte

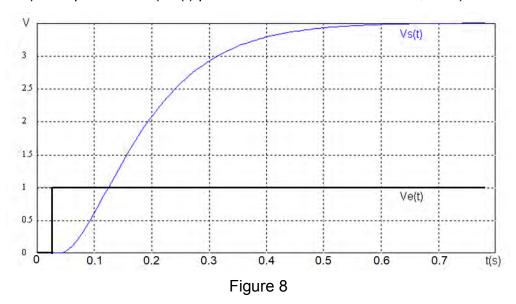

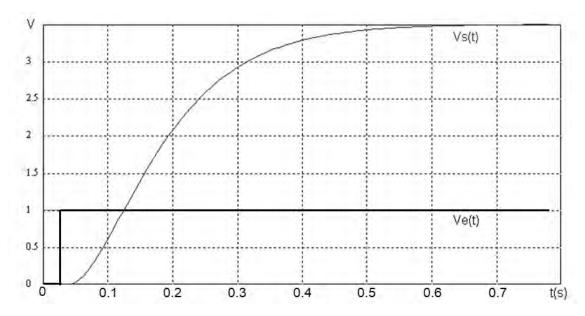

La figure 8 représente Vs(t) la réponse du système (tension proportionnelle à la vitesse du moteur) à un échelon Ve(t) (entrée de commande du hacheur 4 quadrants) d'amplitude 1 V (Ve(t) passe de 0 V à 1 V à l'instant 0,025s).

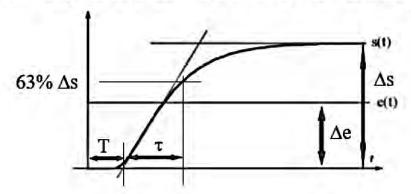

Question C-1 : la méthode de Broïda est présentée en annexe 7. Expliquer et détailler sur le document réponse DR2 les mesures et calculs nécessaires pour établir le modèle.

Identifier alors la fonction de transfert du système sous la forme d'un système du 2<sup>e</sup> ordre.

On suppose, par la suite, afin d'unifier l'identification, que la fonction de transfert en

boucle ouverte est la suivante :

$$F(p) = \frac{Ks}{(1+\tau_1 \cdot p)(1+\tau_2 \cdot p)}$$

Soit avec des valeurs numériques :

$$F(p) = \frac{3.5}{(1+0.2p)(1+0.02p)}$$

L'annexe 8 présente un tableau caractéristique des systèmes du second ordre.

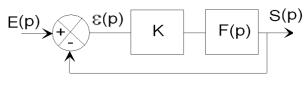

Dans un premier temps, le système est bouclé (figure 9) avec un retour unitaire et un correcteur K (proportionnel) de la manière suivante :

Figure 9

# Résolution algébrique

Question C-2 : calculer la fonction de transfert S(p) / E(p) en boucle fermée en fonction de K, Ks,  $\tau_1$  et  $\tau_2$ . Déterminer ses paramètres principaux (amplification statique, coefficient d'amortissement, pulsation propre) en fonction de K, Ks,  $\tau_1$  et  $\tau_2$ .

Question C-3 : on applique en entrée du système bouclé un échelon unitaire. Choisir K pour avoir un dépassement indiciel (c'est-à-dire le dépassement à un échelon unitaire) en boucle fermée de 20%. Exprimer l'erreur statique et donner sa valeur en % de ∆E où ∆E représente l'amplitude de l'échelon de tension. Tracer l'allure de la réponse temporelle s(t), ainsi que le diagramme de Bode du gain pour la boucle fermée sur le document réponse DR3. On précisera les graduations des axes ainsi que toutes les grandeurs particulières importantes.

# Résolution graphique par l'utilisation du diagramme de Bode

On souhaite résoudre ce même problème mais avec des méthodes graphiques.

Question C-4: tracer sur le document réponse DR4 le diagramme asymptotique de Bode (gain et phase) correspondant à la fonction de transfert F(p). En utilisant la notion de marge de phase, montrer une autre manière de calculer la valeur de K (pour avoir un dépassement indiciel en boucle fermée de 20%). Calculer alors la valeur de K.

Rappel : Il existe une relation empirique qui permet de relier la marge de phase en boucle ouverte et le facteur d'amortissement en boucle fermée.

Cette relation stipule que :

$M\phi_{bo}(^{\circ}) = m_{bf} * 100$  avec  $M\phi_{bo}(^{\circ})$  marge de phase en boucle ouverte en degré, et  $m_{bf}$  coefficient d'amortissement en boucle fermée.

On considèrera qu'elle est valable dans le cas qui nous intéresse.

# Résolution graphique par l'utilisation du diagramme de Black

Le système est bouclé en retour unitaire avec un correcteur proportionnel d'amplification K comme lors de la partie précédente.

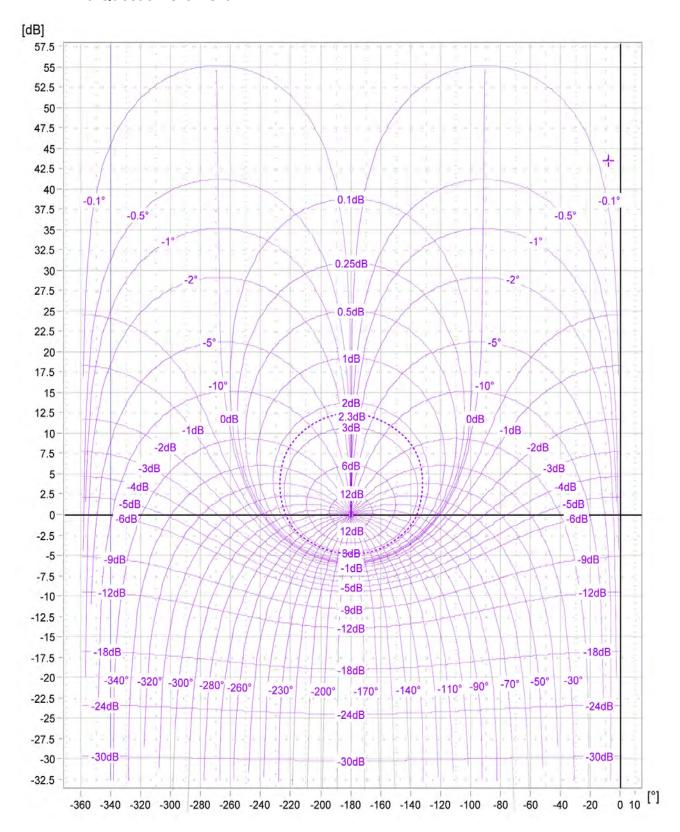

Question C-5 : après avoir construit sur le document réponse DR5 le diagramme de Black correspondant à la fonction de transfert F(p), déterminer, sur ce diagramme, la valeur de K permettant d'obtenir, en boucle fermée, un coefficient d'amortissement du système bouclé de 0,45.

Déterminer graphiquement, pour la boucle fermée, la pulsation de résonance  $\omega_R$  du second ordre équivalent. En déduire en boucle fermée, la pulsation propre  $\omega_0$  et la pulsation de coupure  $\omega_c$ . On expliquera le procédé suivi.

Question C-6 : on se propose d'annuler totalement l'erreur statique. Préciser l'élément à intégrer au correcteur afin d'annuler totalement l'erreur statique. Montrer que la fonction C<sub>PI</sub>(p) qui suit, fonction de transfert d'un correcteur de type proportionnel intégral, satisfait à la condition précédente :

$$C_{PI}(p) = K_{p} \left( 1 + \frac{1}{T_{i} \cdot p} \right) = K_{p} \left( \frac{1 + T_{i} \cdot p}{T_{i} \cdot p} \right)$$

Choisir ses paramètres caractéristiques. On se fixera comme contraintes de compenser la constante de temps dominante du système et d'avoir un coefficient d'amortissement du système bouclé de 0,45.

Représenter sur le document réponse DR5 de la question C-5, la modification apportée par ce correcteur à la fonction de transfert.

# Partie D: analyse de la partie variation de vitesse du robot

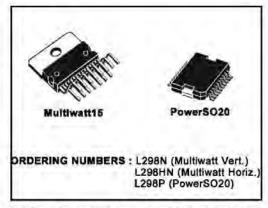

Introduction : pour pouvoir déplacer le robot en vitesse variable, deux versions de hacheurs ont été conçues. La première a été réalisée sur la base d'un composant de puissance intégré. La seconde évolution est basée, en ce qui concerne la transmission de puissance, sur des transistors discrets.

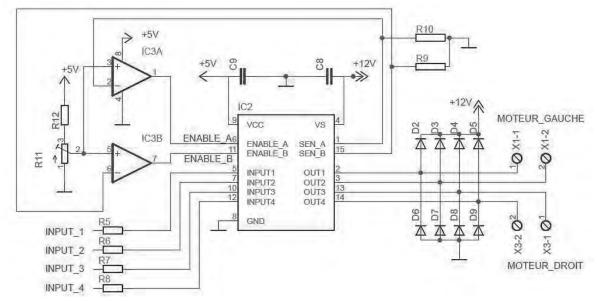

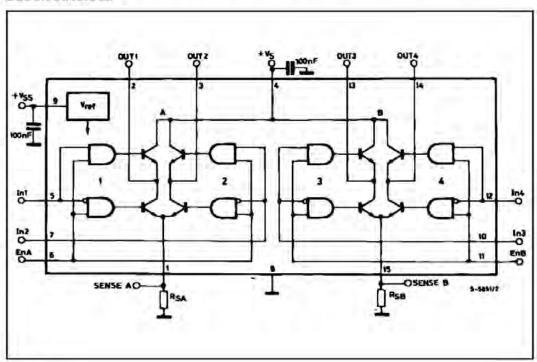

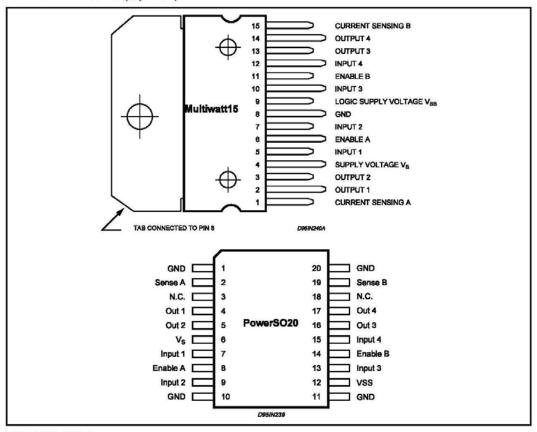

La première version du hacheur 4 quadrants a été réalisée avec les transistors intégrés d'un L298 associé à une limitation de courant comme le présente le schéma qui suit.

Figure 10.

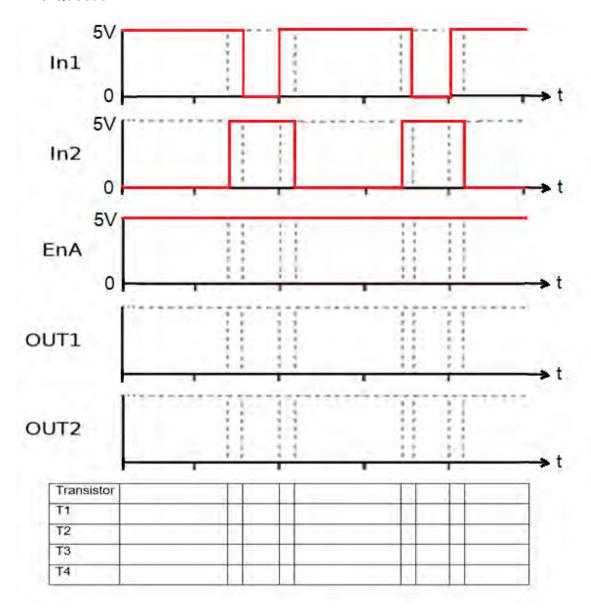

On souhaite déterminer les signaux de sortie du hacheur en fonction des entrées de commande. On se focalisera sur le bras de pont A lié aux broches d'entrée INPUT1, INPUT2 et ENABLE A ainsi qu'aux broches de sortie SEN A, OUT1 et OUT2.

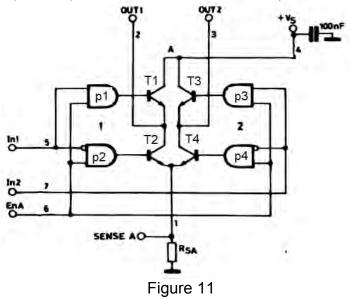

Le schéma interne au L298 est fourni dans la documentation constructeur. On a extrait et complété la partie concernant un bras de pont de ce schéma.

On désire connaître le fonctionnement interne du circuit. Pour ce faire, on va tracer les chronogrammes des divers signaux internes au L298.

Les signaux qui nous intéressent sont In1, In2, EnA, SENSE A, OUT1 et OUT2 de la figure 11.

Pour le tracé, on considère que la résistance  $R_{SA}$  n'a aucune influence, que le circuit est chargé entre OUT1 et OUT2 par une résistance. Les portes logiques internes sont alimentées en Vcc = 5V, l'alimentation de puissance Vs = 12V.

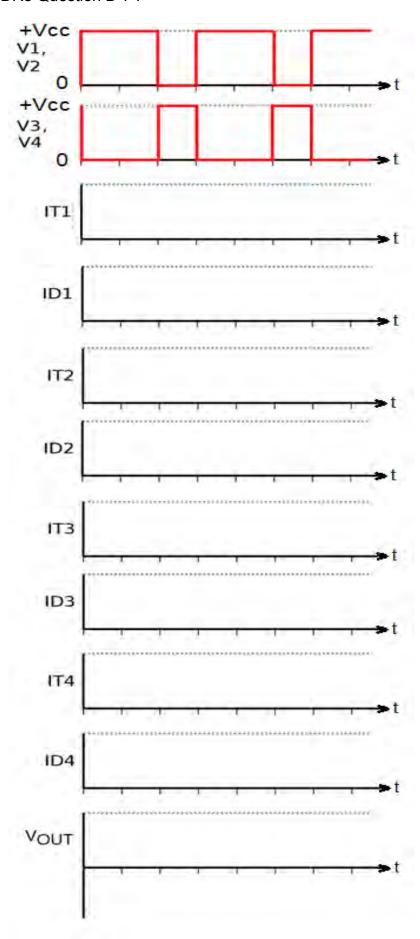

Question D-1 : sur le document réponse DR6, représenter les chronogrammes de fonctionnement pour le cas ou EnA est au niveau logique « 1 ». Compléter les états des transistors sur les intervalles de temps matérialisés lors du fonctionnement. On utilisera la lettre S pour un transistor saturé et B pour bloqué.

Préciser l'état des transistors lorsque EnA est au niveau logique « 0 ». En déduire, en se basant sur les réponses précédentes, la fonction remplie par cette logique de commande.

Le hacheur est maintenant dans sa configuration de fonctionnement sur moteur à courant continu. Le hacheur peut conduire jusqu'à 2A par pont. On partira de cette limite.

Question D-2 : on a choisi une valeur de 0,25  $\Omega$  pour Rsense (soit dans notre cas R9 et R10) utilisée pour la limitation de courant.

Justifier la valeur de Rsense en vous appuyant sur la documentation constructeur du L298 en annexe 9. Calculer la puissance maximum que doit dissiper cette résistance.

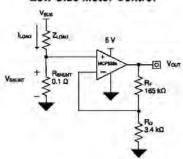

#### Étude de la limitation de courant

En fonctionnement normal, le courant dans le hacheur ne dépasse pas 1,5 A. On souhaite que la limitation de courant soit effective à partir de cette valeur.

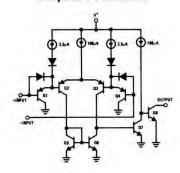

Sur la figure 10, les fonctions comparateur utilisées pour IC3 sont issues du même amplificateur double Rail-to-Rail de référence MC6292 dont un extrait de la documentation technique est fourni en annexe 10.

Question D-3: calculer la valeur des tensions sur les broches 3 et 5 de l'amplificateur en fonction de  $\alpha$ , R11 et R12, avec  $\alpha$ , paramètre lié à la position du curseur de R11 ( $\alpha$  = 0 lorsque les bornes 1 et 2 sont reliées,  $\alpha$  = 1 lorsque les bornes 3 et 2 sont reliées).

Indiquer la raison pour laquelle le concepteur a choisi un amplificateur Rail-to-Rail.

Comme le comportement est le même sur les 2 bras de pont, on ne travaille que sur la partie A.

Question D-4: calculer la valeur du rapport des résistances R11 / R12 qui permettra de limiter le courant à son maximum dans le L298, soit 2 A. Proposer un couple cohérent de valeurs pour R11 et R12 afin que le courant qui circule dans ces deux éléments soit égal à 0,1 mA (on choisira les éléments dans la

série E12, c'est-à-dire parmi les valeurs 1 ; 1,2 ; 1,5 ; 1,8 ; 2,2 ; 2,7 ; 3,3 ; 3,9 ; 4,7 ; 5,6 ; 6,8 ; 8,2).

Préciser ensuite le niveau logique du signal ENABLE\_A en fonction de l'amplitude de la tension aux bornes de R10. Justifier la cohérence du dispositif.

# Calcul de la puissance maximum dissipée dans le L298

Lorsque le hacheur L298 est en fonctionnement dans le robot, soit en fonctionnement sur une machine à courant continu, on a pu constater, dans des cas exceptionnels, un échauffement du L298 qui pourrait conduire à sa destruction. C'est le cas, par exemple, lorsqu'une commande arrive au hacheur, que l'on a demandé au robot d'aller à sa vitesse maximale mais que le robot est arrêté, que les roues ne tournent pas et que la limitation de courant est enclenchée.

On supposera, pour simplifier le calcul, que seuls les transistors participent à l'échauffement et que, lorsque la limitation de courant est enclenchée, le courant qui circule dans le L298 est constant et égal à sa valeur limite maximum de 2 A.

On considère que la température d'une jonction en fonctionnement vaut 135 °C, et que la température ambiante est de 25 °C.

Question D-5 : on se placera dans le cas défini précédemment, et on suppose que les transistors du L298 sont tous identiques. On a mesuré la résistance de la machine à courant continu qui vaut  $R = 4 \Omega$ . Le L298 est en boitier Multiwatt 15. Calculer la puissance dissipée par le L298.

Indiquer la puissance maximale que peut dissiper le L298 sans dissipateur thermique.

Préciser s'il est nécessaire d'adjoindre un dissipateur thermique au L298 et dans l'affirmative, indiquer quelle doit être sa résistance thermique.

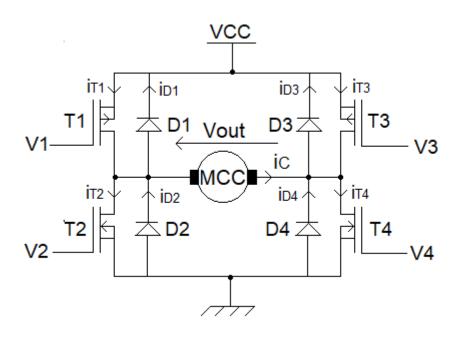

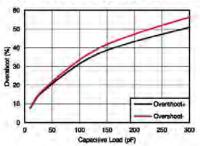

Pour pallier ce problème de limite, on a décidé de réaliser un hacheur 4 quadrants à transistors MOSFET discrets comme le présente la figure qui suit :

Figure 12

Toutes les grandeurs sont variables en fonction du temps.

Question D-6 : compléter le document réponse DR7 avec le type des transistors, le nom des broches, les tensions de commande et les états.

Pour pouvoir dimensionner les éléments constitutifs de ce hacheur, on souhaite déterminer les formes d'ondes de toutes les grandeurs importantes en fonction des entrées de commande des transistors.

Question D-7 : pour le hacheur de la figure 12, on suppose que le courant ic(t) est positif et parfaitement constant, de valeur lc positive pour le tracé des chronogrammes. Les signaux de commandes sont représentés sur le document réponse DR8. Compléter les chronogrammes.

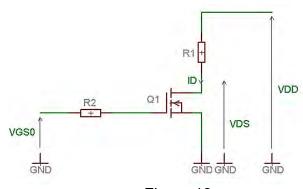

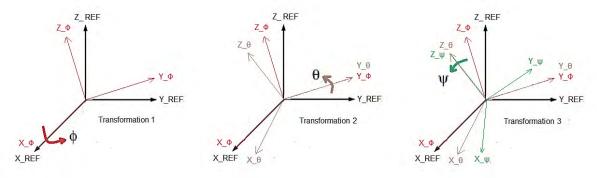

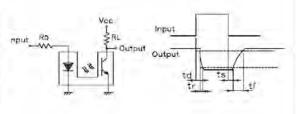

Pour déterminer les pertes dans les transistors MOSFET de puissance, nous allons nous concentrer sur l'un d'entre eux. On considère la structure de test dont le schéma est donné ci-dessous (figure 13) :

Figure 13

De manière simplifiée en figure 14, on peut considérer que les formes d'ondes pour déterminer les pertes sont les suivantes :

Figure 14

On y retrouve les différentes informations temporelles de mise en conduction et de blocage du transistor. On définit les paramètres tr (temps de montée du courant ID), tf (temps de descente du courant ID), tcond et IDM (valeur du courant ID maximum).

Le courant dans le transistor peut être modélisé par une allure trapézoïdale et on peut alors définir les différentes énergies dissipées lors d'une commutation, Eon durant tr, Eoff durant tf et Econd sur la partie entre tr et tf.

Question D-8 : à partir de la figure 14, donner les équations des courant ID(t) et des tensions VDS(t) pour les 3 parties suivantes :

- sur le segment tr

- sur le segment tcond

- sur le segment tf.

Pour les calculs qui suivent, on conservera les équations trouvées pour les segments tret tf. Pour le segment tcond, il sera nécessaire d'améliorer le niveau de modélisation pour la tension VDS(t).

Question D-9: déterminer l'énergie dissipée au moment de la mise en conduction notée Eon, durant la conduction Econd et durant l'ouverture du transistor Eoff, en fonction de tr, tf, RDSon (paramètre du transistor MOS utilisé), IDM et VDD.

Pour un régime permanent du transistor (signal rectangulaire en commande de fréquence f et de rapport cyclique  $\alpha = T_H / T$ ), déterminer la puissance dissipée en fonction des diverses énergies, puis en fonction de toutes les grandeurs précédentes.

Lors d'une campagne de mesures, nous avons déterminé le pire des cas de fonctionnement du hacheur. On a mesuré la puissance maximale dissipée par chaque transistor notée PTmax et la puissance maximale dissipée par chaque diode notée PDmax.

Pour limiter l'échauffement de ces éléments, on associe sur un même dissipateur thermique, à chaque fois, un couple de composants diode et transistor.

Question D-10 : on considère le régime permanent thermique atteint. Déterminer alors le schéma thermique qui permet de modéliser le transfert de chaleur en fonction des diverses puissances, des températures et des résistances thermiques des composants.

Exprimer en fonction des diverses grandeurs, la résistance thermique du dissipateur à choisir.

Une fois cette résistance thermique calculée, indiquer les éléments à prendre en compte pour choisir le dissipateur thermique.

# Partie E: analyse du fonctionnement accéléromètre - gyroscope

Introduction: cette partie concerne l'étage capteur et positionnement (boussole, positionnement IR, centrale gyroscopique et inertielle, et positionnement absolu).

Les données fournies par cet étage permettent au robot d'obtenir sa position absolue sur un terrain à l'aide de 3 balises placées à des endroits connus mais aussi de connaitre son orientation par rapport au sol, ainsi que par rapport au terrain.

Les modules étudiés sont équipés :

- pour l'orientation par rapport au sol, d'un accéléromètre gyroscope MPU6050,

- pour l'orientation sur le terrain, d'une boussole électronique CPMS03,

- pour le positionnement absolu, de 4 modules DW1000, dont 1 sur le robot et 3 utilisés en tant que balises fixes.

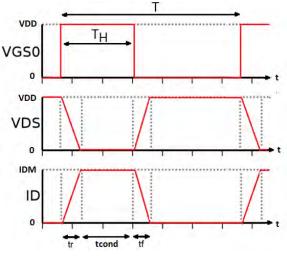

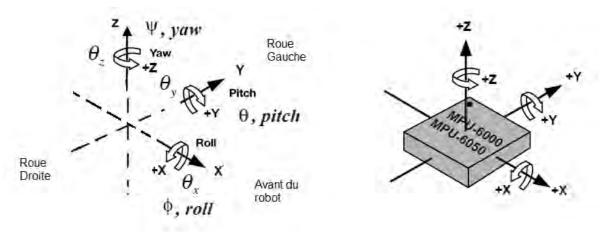

# Étude de l'orientation par rapport au sol - Accéléromètre

La définition des angles utilisés pour caractériser l'attitude du robot (figure 15) est extraite en partie de la documentation constructeur du capteur :

Figure 15

Les termes « roll », « pitch » et « yaw » correspondent respectivement au roulis, tangage et lacet.

Les angles d'Euler  $(\Phi, \theta, \psi)$  correspondent aux diverses rotations autour des axes X (roulis), Y (tangage) et Z (lacet).

On souhaite obtenir, par l'intermédiaire de ce capteur et de la carte électronique qui le met en œuvre, les trois informations angulaires du robot par rapport au sol.

Une position quelconque du robot peut s'apparenter à une combinaison des trois angles de rotation  $\Phi$ ,  $\theta$  et  $\psi$ .

On appellera la base de référence {X\_REF, Y\_REF, Z\_REF}.

Comme le présente la figure 16 qui suit, le passage d'une référence à l'autre se décompose en trois rotations successives des repères :

$\{X_REF, Y_REF, Z_REF\} -> \{X_\Phi, Y_\Phi, Z_\Phi\} -> \{X_\theta, Y_\theta, Z_\theta\} -> \{X_\psi, Y_\psi, Z_\psi\}$

Figure 16

L'accéléromètre fournit 3 grandeurs (acc\_x, acc\_y, acc\_z) qui correspondent à la mesure de la gravité terrestre sur les trois axes dans le repère de l'accéléromètre. Lors d'un déplacement quelconque du robot, il peut y avoir des changements d'orientation sur les trois axes.

Question E-1 : déterminer les trois matrices de rotation  $Rx(\Phi)$ ,  $Ry(\theta)$  et  $Rz(\psi)$  qui correspondent respectivement aux transformations de 1 à 3. En déduire  $Rxyz(\Phi, \theta, \psi) = Rx(\Phi) * Ry(\theta) * Rz(\psi)$ , la matrice totale qui permet de lier le repère final {  $X_{-}\psi, Y_{-}\psi, Z_{-}\psi$  } au repère de référence { $X_{-}REF, Y_{-}REF, Z_{-}REF$ }.

On considèrera, pour simplifier le calcul des angles, que le robot ne se déplace pas. Les grandeurs (acc\_x, acc\_y, acc\_z) mesurées par l'accéléromètre, dans le repère de l'accéléromètre, correspondent alors à la mesure de la gravité terrestre exprimée dans le repère de l'accéléromètre.

(g\_x, g\_y, g\_z) correspondent à la mesure de la gravité terrestre sur les trois axes dans le repère de référence.

Les mesures des accélérations sont algébriques et représentées selon la convention North-East-Down, ce qui signifie que, pour le robot, le repère de référence est orienté pour les axes X\_REF, Y\_REF, Z\_REF respectivement vers le Nord, l'Est et le centre de la terre.

Nous prendrons comme valeurs de la gravité terrestre  $(g_x, g_y, g_z) = (0,0,1)$  où 1 représente une fois la valeur de la gravité terrestre sur l'axe z dans le repère de référence.

Question E-2: exprimer la relation liant (acc\_x, acc\_y, acc\_z),  $Rxyz(\Phi, \theta, \psi)$  et  $(g_x, g_y, g_z)$ , puis développer l'expression précédente afin d'exprimer (acc\_x, acc\_y, acc\_z) en fonction de  $\Phi$ ,  $\theta$  et  $\psi$ . Extraire alors les expressions des différents angles calculables.

# Étude de l'orientation par rapport au sol – Gyroscope - Problème

Dans le cas proposé, le gyroscope fournit la vitesse angulaire autour des trois axes en rad/s.

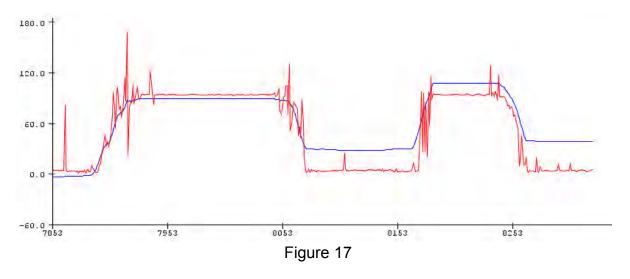

Une campagne de mesures dont on a extrait une partie présente les résultats suivants (figure 17):

Sur l'axe Y du capteur, on a effectué deux rotations de 90 ° avec retour à chaque fois en position initiale. Après implantation des formules de calcul dans un microcontrôleur, la position angulaire calculée grâce au gyroscope correspond à la courbe en bleu, celle calculée par les grandeurs fournies par l'accéléromètre est en rouge.

Question E-3 : conclure et justifier à partir de cette campagne la nécessité de prendre en compte les deux signaux pour obtenir une mesure correcte.

# Combinaison des données avec filtrage numérique pour remédier au problème mis en évidence à la question précédente

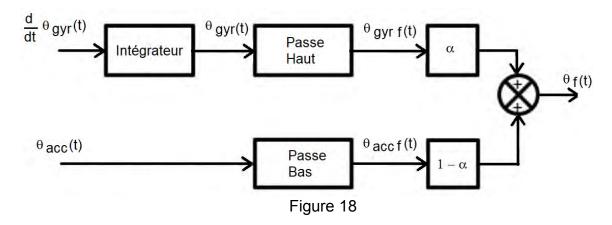

On va donc combiner les données du gyroscope et les données de l'accéléromètre en utilisant le principe de la figure 18.

Le gyroscope fournit une vitesse angulaire notée  $\frac{d\theta_{gyr}(t)}{dt}$

L'accéléromètre fournit un angle θacc(t).

On a choisi de réaliser les deux filtres Passe-Bas et Passe-Haut d'ordre 1 avec une fréquence de coupure de 5 Hz. La fréquence d'échantillonnage choisie est 100 Hz. Ces deux filtres ne réalisent aucune amplification (l'amplification dans la bande passante est égale à 1).

Question E-4 : justifier le synoptique de la figure 18 à partir des résultats obtenus lors de la campagne de mesure.

Calculer ensuite, à partir de l'approximation numérique de la dérivée la plus simple, les équations aux différences des deux filtres utilisés qui seront implantées dans le microcontrôleur, soit  $\theta$ gyrf en fonction de  $\theta$ gyr et  $\theta$ accf en fonction de  $\theta$ acc. En déduire l'expression de  $\theta$ f en prenant en compte  $\alpha$  valeur constante (prorata du Passe-Bas et Passe-Haut).

# Etude du positionnement absolu - Trilatération

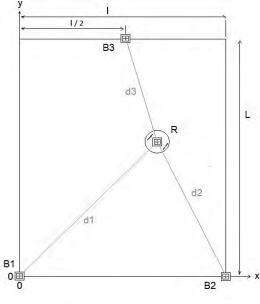

Le robot doit pouvoir se localiser dans l'espace et dans son environnement. On considère que celui-ci est un terrain de longueur L et de largeur l.

Trois balises, disséminées à des positions particulières connues, élaborées à partir de modules DW1000, permettent à un récepteur, lui aussi basé sur un DW1000, situé sur le robot, de connaître sa position par mesure des 3 distances entre le robot et les balises. Un microcontrôleur récupère ces 3 distances et par une série de calculs, élabore la position du robot.

Sur la figure 19, on matérialise les balises B1, B2 et B3 par leur centre. Le récepteur R sur le robot est aussi en son centre. Les distances balises – robot correspondent respectivement à d1, d2 et d3.

# Schéma de principe

Figure 19

La localisation par trilatération utilise la géométrie des cercles.

Le robot est à l'intersection de 3 cercles dont le centre est, à chaque fois, la position de la balise et dont le rayon correspond à la distance entre la balise et le robot.

Question E-5 : dans le repère x, y, donner les coordonnées de chacune des balises et du robot (on affectera aux différentes grandeurs, l'indice 1, 2, 3 ou R, selon qu'elles sont associées respectivement aux balises 1, 2 et 3 et au robot). Exprimer ensuite les coordonnées du robot.

# Partie F: analyse de la fonction élévatrice de tension

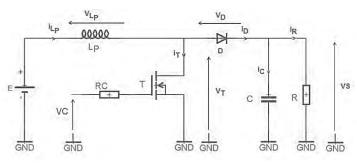

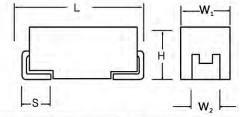

Pour augmenter la vitesse du robot, on propose d'augmenter la tension d'alimentation des moteurs. On utilise un hacheur élévateur ou parallèle, dont on donne le schéma de principe en figure 20.

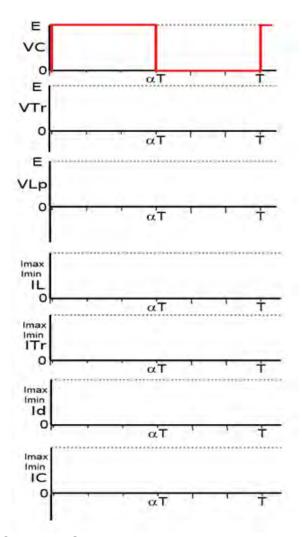

On nomme le transistor T, l'inductance Lp, la diode D et le condensateur C. La résistance R représente la charge du hacheur élévateur. Le paramètre  $\alpha$  représente le rapport cyclique du signal de commande Vc (soit le rapport de la durée au niveau haut du signal de commande divisée par la période de ce même signal).

Figure 20

Question F-1 : en supposant chaque composant idéal et en se plaçant dans le cas d'une conduction continue, en régime permanent, compléter sur le document réponse DR9 les chronogrammes de fonctionnement de l'alimentation. On considérera pour le tracé que la tension  $V_S$  est égale à  $2^*E$  et que le courant dans l'inductance  $L_P$  est compris entre  $I_{max}$  et  $I_{min}$ .

Question F-2: dans le cas général, calculer Vs en fonction de  $\alpha$  et des autres constituants du circuit. En déduire la valeur du rapport cyclique  $\alpha$  permettant de doubler la tension aux bornes de la charge R (ce qui correspondra, dans le cadre de l'utilisation du robot, à doubler la tension d'alimentation des moteurs).

On conservera cette valeur de  $\alpha$  par la suite.

On veut limiter l'ondulation crête à crête de la tension de sortie  $V_s$  du hacheur à  $\Delta Vs = 0,1 V$  pour E = 12 V. La fréquence de découpage est de 30 kHz. On souhaite, de plus, que l'amplitude de l'ondulation du courant dans l'inductance  $L_P$  soit limitée à 200 mA, soit 20% du courant moyen débité par le hacheur.

Question F-3 : déterminer la valeur de l'ondulation de courant ∆I = Imax - Imin et en déduire les valeurs des courants Imax et Imin. Déterminer alors la valeur de l'inductance Lp ainsi que la valeur du condensateur de sortie C (choix dans la série E12).

Question F-4: déterminer l'énergie maximale  $E_{ML}$  stockée par l'inductance  $L_P$  et indiquer où cette énergie est stockée, puis calculer le volume minimal Vmin du circuit magnétique nécessaire pour stocker cette énergie  $E_{ML}$  en limitant l'induction à 200 mT. Déterminer, ensuite, si l'on souhaite limiter la densité de courant  $\delta I$  à 2,5  $A/mm^2$ , le diamètre Df du fil de cuivre que l'on bobinera.

On rappelle que l'énergie maximale  $E_{ML}$  que peut stocker un circuit magnétique de volume effectif V, de perméabilité effective  $\mu_0$  et traversé par une induction

$$B$$

est donnée par :  $E_{ML}=rac{B^2}{2\mu_0}V$  avec  $\mu_0=4*\pi*10^{-7}Hm^{-1}$

Question F-5: à l'aide des documentations des condensateurs en annexe 11, expliquer le choix d'un condensateur aluminium électrolytique ou polymère solide plutôt que celui d'un tantale. Justifier la raison pour laquelle on utilisera pour réaliser l'inductance Lp, un circuit magnétique composé d'une ferrite ou d'un mélange de fer-silicium.

Pour réaliser l'inductance  $L_P$ , on ne bobine pas un conducteur simple, mais une multitude de conducteurs très fins, isolés. Indiquer le phénomène électromagnétique que ce type de bobinage permet d'atténuer et nommer le fil ainsi constitué.

# Partie G: analyse de la fonction odométrie

L'odométrie permet, par la mesure individuelle des déplacements des roues, de connaître la position du robot en mouvement.

On part d'une position initiale connue et, par intégration des déplacements mesurés, on peut déterminer à tous les instants la position du robot.

On désire déterminer un modèle du robot au centre des roues qui nous permettra de piloter celui-ci.

#### Détermination de la vitesse d'une roue du robot

# Rappel:

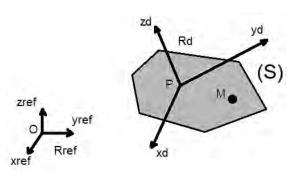

Figure 21

En figure 21, sur un solide indéformable (S), le repère  $R: \left(P, \vec{X}_d, \vec{Y}_d, \vec{Z}_d\right)$  est lié à (S). Si on connaît la vitesse de rotation du solide (S) par rapport au repère référence  $R_0: \left(O, \overrightarrow{X}_{ref}, \overrightarrow{Y}_{ref}, \overrightarrow{Z}_{ref}\right)$ , notée  $\overrightarrow{\Omega}_{S/R_0} = \overrightarrow{\Omega}_{R/R_0}$ , on peut montrer que la vitesse d'un point M du solide est liée à la vitesse du point P par la relation suivante :  $\overrightarrow{V_M} = \overrightarrow{V_P} + \overrightarrow{\Omega}_{S/R_0} \wedge \overrightarrow{PM}$

Noter que dans cette partie, on considère que les vitesses linéaire et de rotation que l'on définira sont déterminées par rapport au référentiel  $R_0$ .

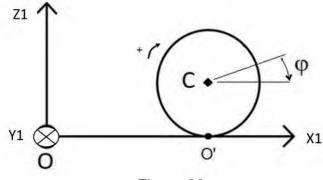

On considère dans ce qui suit le modèle (roue, sol) suivant (figure 22) :

Figure 22

On supposera pour la suite de la modélisation que le contact entre la roue et le sol (au point O') est ponctuel, qu'il n'y a pas de glissement, que les roues ne se déforment pas et on négligera l'épaisseur des roues.

C est le centre de la roue,  $\vec{\varphi}$  est la position angulaire et  $\vec{\Omega}$  est la vitesse angulaire de la roue. On considère  $R_0\left(O,\overrightarrow{X_1},\overrightarrow{Y_1},\overrightarrow{Z_1};t\right)$  le référentiel lié au sol (S<sub>0</sub>) et  $R_1(C, \overrightarrow{X_1}, \overrightarrow{Y_1}, \overrightarrow{Z_1}; t)$  le référentiel lié à la roue (S<sub>1</sub>).

Question G-1 : étant donnée la vitesse du centre de la roue par rapport à R<sub>0</sub> et compte tenu des hypothèses, préciser ce que vaut la vitesse du point O' appartenant à la roue  $\overrightarrow{V}_{O^{\gamma}R_0}$ . En déduire la relation entre la vitesse linéaire du point C et la vitesse angulaire de la roue.

# Détermination d'un modèle du robot au point O<sub>R</sub> placé au centre des roues dans le repère (x,y)

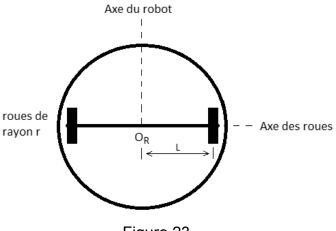

Les dimensions importantes du robot sont fournies sur la figure 23.

Figure 23

On considère maintenant connus :

L : distance entre une roue et le centre  $O_R$  du robot

r : rayon de chacune des roues

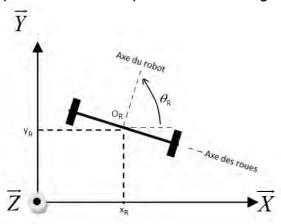

Une position quelconque du robot est représentée sur la figure 24.

Figure 24

$x_R$ ,  $y_R$ ,  $\theta_R$ : posture du robot ou  $x_R$  et  $y_R$  correspondent à la position du robot (position du centre du robot  $O_R$ ) et  $\theta_R$  à l'orientation du robot.

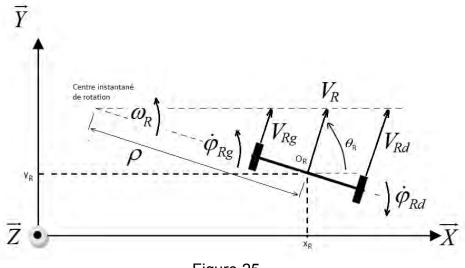

Les grandeurs utilisées pour les calculs sont présentées sur la figure 25.

On appellera  $V_{Rd}$ ,  $V_{Rg}$  et  $V_{R}$ , respectivement, la vitesse linéaire de la roue droite, celle de la roue gauche et celle du centre  $O_R$  du robot.

On appellera  $\phi_{Rd}$ , et  $\phi_{Rg}$ , respectivement, la position angulaire dans le plan de la roue respectivement de la roue droite et de la roue gauche du robot.

$\rho$  correspond à la distance entre le centre instantané de rotation et le centre  $O_R$  du robot et  $\omega_R$  est la vitesse de rotation du robot autour du centre instantané de rotation.

Figure 25

Question G-2 : en considérant un mouvement quelconque, calculer les vitesses linéaires des roues droite et gauche VRd, VRg en fonction de  $\varphi$ d,  $\varphi$ g et r.

Exprimer ensuite les vitesses linéaires des roues droite et gauche VRd, VRg en fonction de  $\rho$ , L et  $\omega_R$ . Extraire des équations précédentes les valeurs de  $\rho$  et de  $\omega_R$ .

Justifier la validité des résultats dans les deux cas limites : le robot va en ligne droite et le robot tourne sur place.

Question G-3 : on considère que la vitesse de rotation du robot autour de son centre de gravité est la même que celle autour de son centre instantané de rotation.

Exprimer la relation liant  $\theta_R$  et  $\omega_R$ .

Donner alors le modèle du robot (valeurs de la vitesse linéaire du centre de gravité et de la vitesse de rotation du robot autour du centre de gravité). En déduire les relations qui lient les dérivées de  $X_R$ ,  $Y_R$ ,  $\theta_R$  à  $V_R$  et  $\omega_R$ .

Question G-4: proposer un algorithme qui permettrait d'implanter cette odométrie dans le robot.

#### Dimensionnement des éléments utiles au fonctionnement du capteur.

Pour pouvoir renseigner le robot avec son odométrie, il faut mesurer la vitesse des roues.

Au niveau mécanique, pour une roue, le système de mesure est constitué d'un disque et de deux capteurs optiques à fourche décalés par rapport au disque. Ces deux capteurs vont nous permettre d'obtenir 2 signaux que l'on nommera A et B. Le signal A est un signal carré dont la fréquence sera proportionnelle à la vitesse. Le signal B, quant à lui, à la même forme que le signal A mais est décalé de + ou – un quart de période suivant le sens de rotation de la roue.

On s'intéresse à la partie électronique et plus particulièrement à la façon d'élaborer les signaux carrés et à leur mise en forme.

La structure utilisée est celle présentée sur le schéma suivant (figure 26) et correspond à un seul des capteurs :

Figure 26

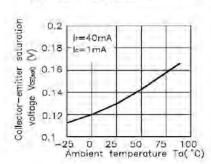

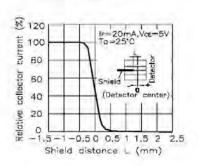

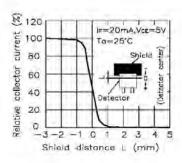

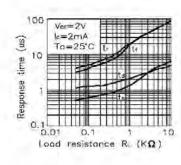

Les capteurs utilisés sont des KTIR0611S dont la documentation est fournie en annexe 12. La documentation du LM393 est fournie en annexe 13.

L'alimentation Vcc de la structure est de 5 V. La LED du capteur à fourche est parcourue par un courant de 20 mA. Le transistor de sortie du capteur doit être juste saturé lorsque le disque n'obture pas la lumière transmise.

Question G-5 : calculer les valeurs des résistances R1 et R2. Calculer l'amplitude de la tension VIm293, sachant que les deux résistances R3 et R4 sont identiques. Préciser alors la fonction remplie par le composant IC1A. Justifier la valeur choisie de 10 K $\Omega$  pour la résistance R5.

Remplir le tableau du document réponse DR9 concernant Vco et Vout pour les deux positions principales du disque.

# Utilisation de l'odométrie pour asservir le robot

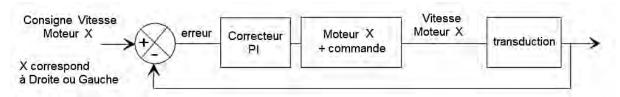

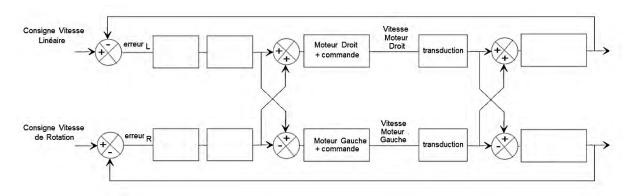

Connaissant les vitesses des roues droite et gauche par l'intermédiaire du système de mesure, on pourrait asservir directement les deux vitesses, comme le présente le schéma de principe suivant (figure 27) :

Figure 27

Cette méthode d'asservissement fonctionne, mais est perfectible.

Comme on a calculé précédemment en fonction du modèle du robot, la valeur de la vitesse linéaire du robot ainsi que sa vitesse de rotation autour de son centre de gravité, on préfère asservir ces deux grandeurs.

Question G-6 : en complétant le document réponse DR9, modéliser le double asservissement de la valeur de la vitesse linéaire et de la vitesse de rotation qui sera implanté dans le robot.

# Partie H: analyse d'un code programmé

Introduction: Elaboration du code par génération automatique avec Matlab Simulink.

Toutes les cartes du robot contiennent des microcontrôleurs. Le langage de programmation utilisé pour la programmation de toutes les cartes est le langage C. Certaines de ces cartes ont été programmées directement en langage C. Pour d'autres, on a utilisé un système de génération de code automatique.

Des extraits de la documentation du microcontrôleur dsPIC 30F4011 sont fournis en annexe 14.

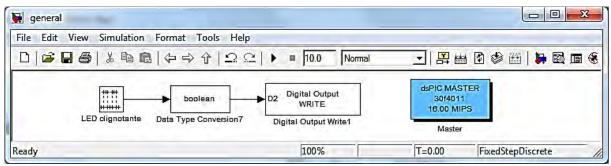

La méthode consiste à réaliser le schéma bloc, dans Matlab Simulink (figure 28), d'une boucle du programme principal comme le présente le schéma suivant :

Figure 28

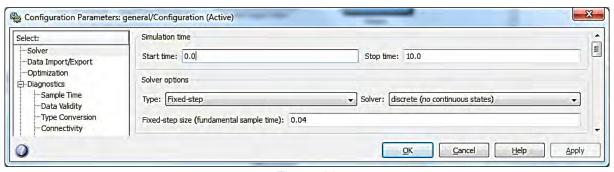

Une autre fenêtre de paramètres (figure 29) est importante :

Figure 29

Celle-ci précise la période de répétition du programme soit ici une exécution toute les 0,04 s (notée « fundamental sample time »).

Dans la figure 28, le bloc dsPIC MASTER indique le type de microcontrôleur utilisé, ici un dsPIC 30F4011 et par l'intermédiaire de la valeur en MIPS, la manière dont est gérée sa fréquence d'horloge (ici le nombre d'instructions exécutées par seconde est de 16000000 soit 16MIPS).

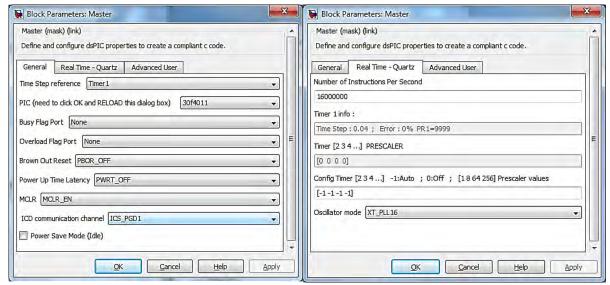

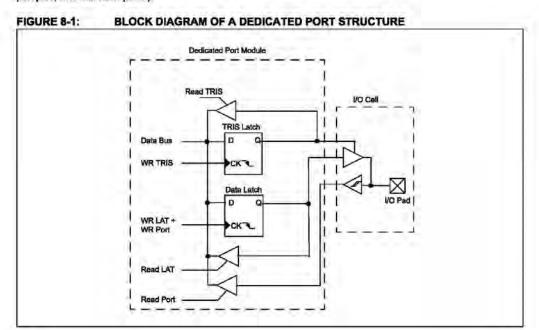

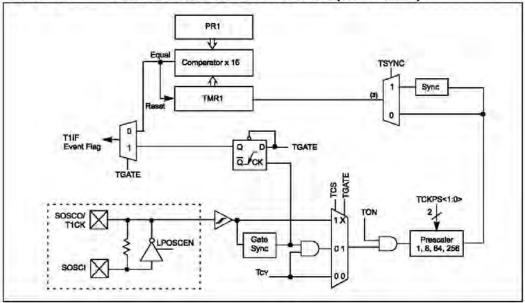

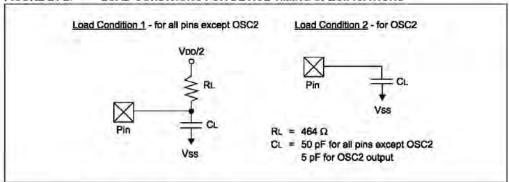

Si on regarde en détails (Figures 30 et 30bis) ce que contient ce bloc, on retrouve la configuration de l'oscillateur du dsPIC.

Figure 30 Figure 30bis

Dans le cas présent, le dsPIC fonctionne sur la base d'un quartz 4MHz (mode XT).

Sur les figures 30 et 30bis, on peut noter que le cadencement de la boucle principale du programme est effectué par le Timer1 et, de plus, que l'on a mis en route la boucle à verrouillage de phase (XT PLL16) en mode x 16.

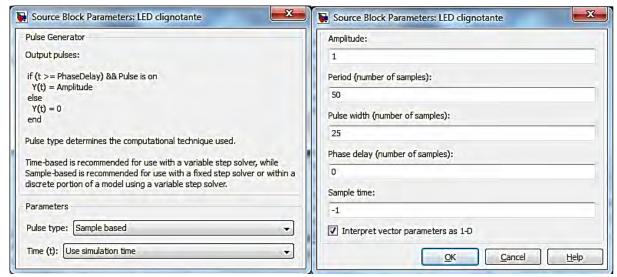

Dans la fenêtre figure 28, les 3 blocs (LED clignotante, Data Type Conversion7 et Digital Output Write1) représentent un pas de calcul. Dans ce cas, comme exemple, on désire faire clignoter une led connectée par l'intermédiaire d'une résistance sur la broche 2 du port D qui en contient 4 référencées de RD0 à RD3.

Les configurations choisies pour le générateur sont présentées en figure 31 :

Figure 31

Le paramètre Sample time égal à -1 signifie que le générateur est cadencé à la vitesse de la boucle principale soit 0,04 s.

La génération automatique de code de Matlab Simulink fournit alors, comme code correspondant à l'application, le résultat proposé dans le document réponse DR10.

- Question H-1: compléter les cases vides du document réponse DR10 en proposant les commentaires du code généré.

- Question H-2 : justifier, par l'étude du fonctionnement du Timer1, la période de répétition de la boucle de 0,04 s.

Calculer la valeur de la fréquence du signal présent sur RD2. Justifier ce résultat sur la base du code fourni et de la vitesse de la boucle principale de 0,04 s.

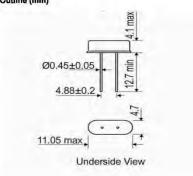

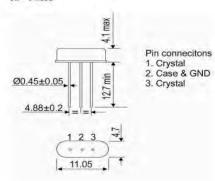

### **Crystal Specification** Model: HC49/4H

### ISSUE 15; September 2012 - RoHS 2011/65/EU

■ Industry standard leaded package Resistance welded, hermetically sealed in an inert atmosphere, glass to metal seals on leads

Variants available include but are not limited to -3L = a centre mounted third leg grounds the can

Low profile versions available please contact our sales offices for

Please see our HC49/4HSMX for a SMD alternative

### Frequency Range

3.2 to 100.0MHz Frequency ■ Frequency Stability ±15.00ppm ■ Frequency Tolerance ±10ppm to ±100ppm

**General Specification** ■ Load Capacitance (CL) 10.0pF to 75.0pF or Series

■ Drive Level Ageing ±5ppm typical per year at 25°C

500uW max

■ Shunt Capacitance (C0) 7pF max

### **Operating Temperature Ranges**

- 0 to 50°C

- -10 to 60°C

- -20 to 70°C

- -30 to 80°C

- -40 to 85°C

- -55 to 105°C

#### Frequency Parameters

■ Ageing: ±1ppm available on request

#### **Environmental Parameters**

- Storage Temperature Range: -55 to 125°C

- Shock: 981m/s², 6ms, 3 times in each of 3 mutually perpendicular

- Vibration: 10Hz-60Hz, 0.75mm amplitude, 60Hz-500Hz, 98.1m/s², 30mins in 3 mutually perpendicular planes

### **Ordering Information**

Frequency\*

Frequency Tolerance (@ 25°C)\*

Frequency Stability (over operating temperature range)\*

Operating Temperature Range\*

Load Capacitance\* Overtone\*

(\*minimum required)

Example

10.0MHz HC49/4H

50/50/-40 to 85C/10 FUND

■ Pack Style: Bulk Loose in Bulk pack

Pack Size

Pack Style: Reel Tape and reel in accordance with EIA-468-C

Pack Size

#### Outline (mm)

### -3L = 3 Lead

### Sales Office Contact Details:

UK: +44 (0)1460 270200 Germany: +49 (0)7264 9145-0 France: +33 (0)5 34 50 91 18 USA: +1 (0)408.273.4530

Email: info@iqdfrequencyproducts.com Web: www.iqdfrequencyproducts.com

Printed on 3 Oct 12 17:15

Page 1 of 3

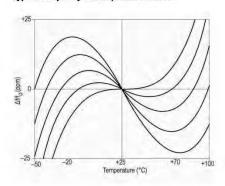

## Crystal Specification Model: HC49/4H

■ Alternative packing options available

### Typical Frequency vs Temperature Curves

#### **Electrical Specification - maximum limiting values**

| Frequency<br>Range | Frequency<br>Tolerance | Stat                                                      | oility  | Temperature<br>Range                                                                  | ESR Max | Vibration<br>Mode |

|--------------------|------------------------|-----------------------------------------------------------|---------|---------------------------------------------------------------------------------------|---------|-------------------|

|                    |                        | Min                                                       | Max     |                                                                                       |         | 1,000             |

| 3.2 to <4.0MHz     | ±10ppm to ±100ppm      | ±15ppm<br>±20ppm<br>±20ppm<br>±25ppm<br>±30ppm<br>±100ppm | ±500ppm | 0 to 50°C<br>-10 to 60°C<br>-20 to 70°C<br>-30 to 80°C<br>-40 to 85°C<br>-55 to 105°C | 300Ω    | Fundamental       |

| 4.0 to <5.5MHz     | ±10ppm to ±100ppm      | ±15ppm<br>±20ppm<br>±20ppm<br>±25ppm<br>±30ppm<br>±100ppm | ±500ppm | 0 to 50°C -10 to 60°C -20 to 70°C -30 to 80°C -40 to 85°C -55 to 105°C                | 130Ω    | Fundamental       |

| 5.5 to <8.0MHz     | ±10ppm to ±100ppm      | ±15ppm<br>±20ppm<br>±20ppm<br>±25ppm<br>±30ppm<br>±100ppm | ±500ppm | 0 to 50°C -10 to 60°C -20 to 70°C -30 to 80°C -40 to 85°C -55 to 105°C                | 60Ω     | Fundamental       |

| 8.0 to <40.0MHz    | ±10ppm to ±100ppm      | ±15ppm<br>±20ppm<br>±20ppm<br>±25ppm<br>±30ppm<br>±100ppm | ±500ppm | 0 to 50°C<br>-10 to 60°C<br>-20 to 70°C<br>-30 to 80°C<br>-40 to 85°C<br>-55 to 105°C | 40Ω     | Fundamental       |

| 26.0 to <100.0MHz  | ±10ppm to ±100ppm      | ±15ppm<br>±20ppm<br>±20ppm<br>±25ppm<br>±30ppm<br>±100ppm | ±500ppm | 0 to 50°C -10 to 60°C -20 to 70°C -30 to 80°C -40 to 85°C -55 to 105°C                | 100Ω    | 3RD Overtone      |

Sales Office Contact Details:

UK: +44 (0)1460 270200 Germany: +49 (0)7264 9145-0 France: +33 (0)5 34 50 91 18 USA: +1 (0)408.273.4530

Email: info@iqdfrequencyproducts.com Web: www.iqdfrequencyproducts.com

Printed on 3 Oct 12 17:15

Page 2 of 3

### dsPIC33F Family Reference Manual

### Register 48-1: FOSCSEL: Oscillator Source Selection Register

| U      | U | U | U | U | Ü | U | U     |

|--------|---|---|---|---|---|---|-------|

| -      | - | - | - | - | - | - | -     |

| bit 15 |   |   |   |   |   |   | bit 8 |

| R/P  | U | U-0 | u | U | R/P | R/P        | R/P |

|------|---|-----|---|---|-----|------------|-----|

| IESO | - | -   | - | - |     | FNOSC<2:0  |     |

| it 7 |   |     |   | V |     | - B. A. A. | bit |

Legend:

R = Readable bit P = Programmable bit U = Unused bits, program to Logic '1'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 Reserved: Reserved bits must be programmed as '1'

bit 7 IESO: Internal External Start-up Option bit

1 = Start device with internal FRC, and then automatically switch to the user-selected oscillator source when ready

o = Start device with user-selected oscillator source

bit 6 Reserved: Reserved bits must be programmed as '1'

bit 5 Unimplemented: Read as '0'

bit 4-3 Reserved: Reserved bits must be programmed as '1'

bit 2-0 FNOSC<2:0>: Initial Oscillator Source Selection bits 111 = Fast RC oscillator with Divide-by-N (FRCDIVN)

110 = Fast RC oscillator with Divide-by-16 (FRCDIV16)

101 = Low-Power RC oscillator (LPRC)

100 = Secondary oscillator (Sosc)

011 = Primary oscillator with PLL (XTPLL, HSPLL, ECPLL)

010 = Primary oscillator (XT, HS, EC)

001 = Fast RC oscillator with PLL (FRCPLL)

000 = Fast RC oscillator (FRC)

### Section 48. Oscillator (Part V)

#### Register 48-2: FOSC: Oscillator Configuration Register

| U      | U | U | U | U | U | U | U     |

|--------|---|---|---|---|---|---|-------|

| -      | - | - | - | - | - | - | -     |

| bit 15 |   |   |   |   |   |   | bit 8 |

| R/P   | R/P    | R/P     | Ų | U | R/P      | R/P   | R/P     |

|-------|--------|---------|---|---|----------|-------|---------|

| FCKS  | M<1:0> | IOL1WAY | - | - | OSCIOFNC | POSCA | AD<1:0> |

| oit 7 |        |         |   |   |          |       | t       |

| - | _ |   |   | _  | 1 |

|---|---|---|---|----|---|

|   | _ | _ | _ | -1 | ١ |

|   | а |   | п | а  |   |

|   |   |   |   |    |   |

| Lugeria.          |                      |                        |                    |

|-------------------|----------------------|------------------------|--------------------|

| R = Readable bit  | P = Programmable bit | U = Unused bits, progr | ram to Logic '1'   |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 Reserved: Reserved bits must be programmed as '1'

bit 7-6 FCKSM<1:0>: Clock Switching Mode bits

1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled 00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled

bit 5 IOL1WAY: Peripheral Pin Select Configuration bit (1)

1 = Allow only one reconfiguration

0 = Allow multiple reconfigurations

bit 4-3 Reserved: Reserved bits must be programmed as '1'

bit 2 OSCIOFNC: OSC2 Pin Function bit (except in XT and HS modes)

1 = OSC2 is clock output and instruction cycle (Fcy) clock is output on OSC2 pin

0 = OSC2 is a general purpose digital I/O pin

bit 1-0 POSCMD<1:0>: Primary Oscillator Mode Selection bits

11 = Primary oscillator is disabled

10 = HS (High-Speed) Crystal oscillator mode

01 = XT (Crystal) oscillator mode

00 = EC (External Clock) mode

4 Oscillato

Note 1: The IOL1WAY bit is not available on all dsPIC33F devices. Refer to the specific device data sheet for more information.

### dsPIC33F Family Reference Manual

#### 48.4 SPECIAL FUNCTION REGISTERS (SFRs)

These Special Function Registers provide run-time control and status of the oscillator system:

#### · OSCCON: Oscillator Control Register

The Oscillator Control (OSCCON) register controls clock switching and provides status information that allows the current clock source, PLL lock, and clock fail conditions to be monitored.

#### · CLKDIV: Clock Divisor Register

The Clock Divisor (CLKDIV) register controls Doze mode and selects the PLL prescaler, PLL postscaler and FRC postscaler.

#### PLLFBD: PLL Feedback Divisor Register

The PLL Feedback Divisor (PLLFBD) register selects the PLL feedback divisor.

### · OSCTUN: Oscillator Tuning Register

The FRC Oscillator Tuning (OSCTUN) register is used to tune the frequency of the internal FRC oscillator from -12% to +11.625% (30 kHz steps) of the nominal frequency value. The nominal or tuned frequency of the FRC oscillator is expected to remain within  $\pm$  2% of the tuned value over the temperature and voltage variations of a particular device.

#### OSCTUN2: Oscillator Tuning Register 2

The OSCTUN and the OSCTUN2 registers enable the PWM to operate in Frequency Sequencing mode. These registers allow the user application to select a sequence of eight different FRC TUN values to vary the system frequency with each rollover of the primary PWM time base.

#### · LFSR: Linear Feedback Shift Register

The Linear Feedback Shift Register is used to implement the Pseudo Random Clock Dither (PRCD) logic.

### · ACLKCON: Auxiliary Clock Control Register

The Auxiliary Clock Control (ACLKCON) register controls the auxiliary PLL mode and the auxiliary PLL clock divider.

#### · REFOCON: Reference Oscillator Control Register

The reference clock output provides a clock signal to any remappable pin (RPx). The reference clock can be either the external oscillator or the system clock.

Note: The Oscillator Special Function Registers (OSCCON, CLKDIV, PLLFBD, OSCTUN, and ACLKCON) are reset only on Power-on Reset.

### Section 48. Oscillator (Part V)

#### Register 48-3: OSCCON: Oscillator Control Register

| U-0               | R-0 | R-0       | R-0 | U-O | R/W-y | R/W-y     | R/W-y |

|-------------------|-----|-----------|-----|-----|-------|-----------|-------|

| , <del>=</del> ,= |     | COSC<2:0> |     | _   |       | NOSC<2:0> |       |

| it 15             | •   |           |     |     |       |           | bit   |

| R/W-0   | U-0              | R-0  | R/W-0  | R/C-0 | R/W-0  | R/W-0   | R/W-0 |

|---------|------------------|------|--------|-------|--------|---------|-------|

| CLKLOCK | 0 <del>-</del> 0 | LOCK | PRCDEN | CF    | TSEQEN | LPOSCEN | OSWEN |

| bit 7   |                  |      | 1      |       |        |         | bit   |

| Legend:           | y = Value set from Co | y = Value set from Configuration bits on POR |                    |  |  |

|-------------------|-----------------------|----------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit                        | read as '0'        |  |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared                         | x = Bit is unknown |  |  |

bit 15 Unimplemented: Read as '0'

bit 14-12 COSC<2:0>: Current Oscillator Selection bits (read-only)

111 = Fast RC oscillator (FRC) with Divide-by-N 110 = Fast RC oscillator (FRC) with Divide-by-16

101 = Low-Power RC oscillator (LPRC) 100 = Secondary oscillator (Sosc)

011 = Primary oscillator (XT, HS, EC) with PLL

010 = Primary oscillator (XT, HS, EC) 001 = Fast RC oscillator (FRC) with PLL 000 = Fast RC oscillator (FRC)

bit 11 Unimplemented: Read as '0'

bit 10-8 NOSC<2:0>: New Oscillator Selection bits

111 = Fast RC oscillator (FRC) with Divide-by-N 110 = Fast RC oscillator (FRC) with Divide-by-16

101 = Low-Power RC oscillator (LPRC) 100 = Secondary oscillator (Sosc)

011 = Primary oscillator (XT, HS, EC) with PLL 010 = Primary oscillator (XT, HS, EC) 001 = Fast RC oscillator (FRC) with PLL

000 = Fast RC oscillator (FRC)

bit 7 CLKLOCK: Clock Lock Enable bit

If clock switching is enabled and FSCM is disabled, (FOSC<FCKSM> = 0b01):

1 = Clock switching is disabled, system clock source is locked

o = Clock switching is enabled, system clock source can be modified by clock switching

bit 6 Unimplemented: Read as '0'

bit 5 LOCK: PLL Lock Status bit (read-only)

1 = Indicates that PLL is in lock, or PLL start-up timer is satisfied

0 = Indicates that PLL is out of lock, start-up timer is in progress or PLL is disabled

bit 4 PRCDEN: Pseudo Random Clock Dither Enable bit

1 = Pseudo random clock dither is enabled 0 = Pseudo random clock dither is disabled

bit 3 CF: Clock-Fail Detect bit (read/clear by application)

1 = FSCM has detected clock failure 0 = FSCM has not detected clock failure

bit 2 TSEQEN: FRC Tune Sequencer Enable bit

1 = The TUN<3:0>, TSEQ1<3:0>, ..., TSEQ7<3:0> bits in the OSCTUN and the OSCTUN2 registers sequentially tune the FRC oscillator. Each field being sequentially selected via the ROLL<2:0> signals from the PWM module.

a = The TUN<3:0> bits in the OSCTUN register tune the FRC oscillator

© 2009 Microchip Technology Inc.

Preliminary

DS70596A-page 48-9

### dsPIC33F Family Reference Manual

Register 48-3: OSCCON: Oscillator Control Register (Continued)

bit 1 LPOSCEN: Secondary (LP) Oscillator Enable bit

Enable secondary oscillator

Disable secondary oscillator

SWEN: Oscillator Switch Enable bit

1 = Request oscillator switch to selection specified by NOSC<2:0> bits

0 = Oscillator switch is complete

Note: Writes to this register requires an unlock sequence. For details and examples refer to 48.12 "Clock

Switching".

bit 0

## 48 Oscill

### Section 48. Oscillator (Part V)

### Register 48-4: CLKDIV: Clock Divisor Register

| R/W-0 | R/W-0 | R/W-1     | R/W-1 | R/W-0    | R/W-0 | R/W-0       | R/W-0 |

|-------|-------|-----------|-------|----------|-------|-------------|-------|

| ROI   |       | DOZE<2:0> |       | DOZEN(1) | 7     | FRCDIV<2:0> |       |

| 15    |       |           |       |          |       |             | bit   |

| R/W-0  | R/W-1   | U-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|---------|-----|-------------|-------|-------|-------|-------|

| PLLPOS | ST<1:0> | -   | PLLPRE<4:0> |       |       |       |       |

| oit 7  |         |     |             |       |       |       | bit ( |

| Legend:           | 773.32           | - 13.2000             | Y. Water Town      |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15 ROI: Recover on Interrupt bit

1 = Interrupts will clear the DOZEN bit and the processor clock/peripheral clock ratio is set to 1:1

o = Interrupts have no effect on the DOZEN bit

bit 14-12 DOZE<2:0>: Processor Clock Reduction Select bits

111 = FcY divided by 128 110 = FcY divided by 64 101 = FcY divided by 32 100 = FcY divided by 18 011 = FcY divided by 8 (default) 010 = FcY divided by 4 001 = FcY divided by 2 000 = FcY divided by 1

bit 11 DOZEN: DOZE Mode Enable bit(1)

1 = DOZE<2:0> field specifies the ratio between the peripheral clocks and the processor clocks

o = Processor clock/peripheral clock ratio forced to 1:1

bit 10-8 FRCDIV<2:0>: Internal Fast RC Oscillator Postscaler bits

111 = FRC divided by 256 110 = FRC divided by 64 101 = FRC divided by 32 100 = FRC divided by 16 011 = FRC divided by 8 010 = FRC divided by 4 001 = FRC divided by 2 000 = FRC divided by 1 (default)

bit 7-6 PLLPOST<1:0>: PLL VCO Output Divider Select bits (also denoted as 'N2', PLL postscaler)

11 = Output divided by 8 10 = Reserved 01 = Output divided by 4 (default)

00 = Output divided by 2

bit 5 UnImplemented: Read as '0'

bit 4-0 PLLPRE<4:0>: PLL Phase Detector Input Divider Select bits (also denoted as 'N1', PLL prescaler)

11111 = Input divided by 33

number of the state of the st

00000 = input divided by 2 (default)

00001 = Input divided by 3

Note 1: This bit is cleared when the ROI bit is set and an interrupt occurs.

Refer to Section 9. "Watchdog Timer and Power-Saving modes" (DS70196) in the "dsPIC33F Family Reference Manual" for more information on Doze mode.

© 2009 Microchip Technology Inc.

Preliminary

DS70596A-page 48-11

### dsPIC33F Family Reference Manual

### Register 48-5: PLLFBD: PLL Feedback Divisor Register

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0     |

|--------|-----|-----|-----|-----|-----|-----|-----------|

| _      | _   | _   | _   | _   | _   | _   | PLLDIV<8> |

| bit 15 |     |     |     |     |     |     | bit 8     |

| R/W-0       | R/W-0 | R/W-1 | R/W-1 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|

| PLLDIV<7:0> |       |       |       |       |       |       |       |  |

| bit 7       |       |       |       |       |       |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-9 Unimplemented: Read as '0'

bit 8-0 PLLDIV<8:0>: PLL Feedback Divisor bits (also denoted as 'M', PLL multiplier)

111111111 = 513

•

.

000110000 = 50 (default)

•

•

-

000000010 = 4

000000001 = 3

000000000 = 2

### Section 21. ECANTM

### HIGHLIGHTS

This section of the manual contains the following major topics:

| 21.1 Introduction                            | 21-2    |

|----------------------------------------------|---------|

| 21.2 CAN Message Formats                     | 21-4    |

| 21.3 ECAN Registers                          | 21-9    |

| 21.4 ECAN Message Buffers                    | . 21-30 |

| 21.5 ECAN Operating Modes                    | .21-34  |

| 21.6 Transmitting EGAN Messages              | .21-35  |

| 21.7 Receiving ECAN Messages                 | .21-41  |

| 21.8 DMA Controller Configuration            | . 21-53 |

| 21.9 Bit Timing                              | .21-56  |

| 21.10 ECAN Error Management                  | .21-60  |

| 21.11 ECAN Interrupts                        | .21-63  |

| 21.12 ECAN Low-Power Modes                   | .21-66  |

| 21.13 ECAN Time Stamping Using Input Capture | .21-66  |

| 21.14 Register Maps                          | .21-66  |

| 21.15 Related Application Notes              | .21-73  |

| 21 16 Revision History                       | 21-74   |

© 2007-2012 Microchip Technology Inc.

DS70185C-page 21-1

### dsPIC33F/PIC24H Family Reference Manual

Note

This family reference manual section is meant to serve as a complement to device data sheets. Depending on the device variant, this manual section may not apply to all dsPIC33F/PIC24H devices.

Please consult the note at the beginning of the "Direct Memory Access (DMA)" chapter in the current device data sheet to check whether this document supports the device you are using.

Device data sheets and family reference manual sections are available for download from the Microchip Worldwide Web site at: http://www.microchip.com

### 21.1 INTRODUCTION

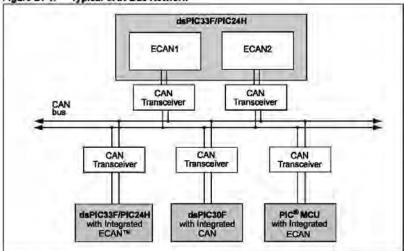

The dsPIC33F/PIC24H Enhanced Controller Area Network (ECAN™) module implements the CAN Protocol 2.0B, used primarily in industrial and automotive applications. This asynchronous serial data communication protocol provides reliable communications in electrically noisy environments. The dsPIC33F device family integrates up to two ECAN modules. Figure 21-1 Illustrates a typical CAN bus topology.

Figure 21-1: Typical CAN Bus Network

The ECAN module supports the following key features:

### Standards Compliance:

- Full CAN 2.0B compliance

- · Programmable bit rate up to 1 Mbps

### Message Reception:

- · 32 message buffers all of them can be used for reception

- 16 acceptance filters for message filtering

- Three acceptance filter mask registers for message filtering

- Automatic response to Remote Transmit Request

- Up to 32-message deep First In First Out (FIFO) buffer

- DeviceNet™ addressing support

- · DMA interface for message reception

#### Message Transmission:

- · Eight message buffers configurable for message transmission

- User-defined priority levels for message buffers used for transmission

- DMA interface for message transmission

#### Others:

- Loopback, Listen All Messages, and Listen Only modes for self-test, system diagnostics, and bus monitoring

- · Low-power operating modes

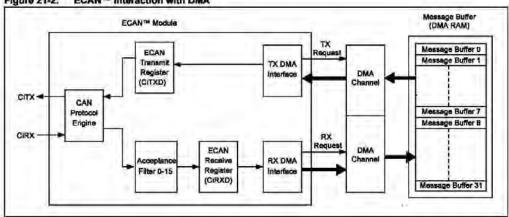

Figure 21-2 illustrates the general structure of the ECAN module and its interaction with the DMA Controller and DMA RAM.

Figure 21-2: ECAN™ Interaction with DMA

#### 21.1.1 ECAN Module

The ECAN module consists of a protocol engine, message acceptance filters, and separate transmit and receive DMA interfaces. The protocol engine transmits and receives messages to and from the CAN bus (as per CAN bus 2.0B protocol). The user-configurable acceptance filters are used by the module to examine the received message to determine if it should be stored in the DMA message buffer or discarded.

For received messages, the receive DMA interface generates a receive data interrupt to initiate a DMA cycle. The receive DMA channel reads data from the CiRXD register and writes it into the message buffer.

For transmit messages, the transmit DMA interface generates a transmit data interrupt to start a DMA cycle. The transmit DMA channel reads from the message buffer and writes to the CiTXD register for message transmission.

### 21.1.2 Message Buffers

The ECAN module supports up to 32 message buffers for storing data transmitted or received on the CAN bus. These buffers are located in DMA RAM. Message buffers 0-7 can be configured for either transmit or receive operation. Message buffers 8-31 are receive-only buffers and cannot be used for Message Transmission.

### 21.1.3 DMA Controller

The DMA controller acts as an interface between the message buffers and ECAN to transfer data back and forth without CPU intervention. The DMA controller supports up to eight channels for transferring data between DMA RAM and the dsPIC33F peripherals. Two separate DMA channels are needed to support CAN message transmission and CAN message reception.

Each DMA channel has a DMA Request register (DMAxREQ), which is used by the user application to assign an interrupt event to trigger a DMA-based message transfer.

### dsPIC33F/PIC24H Family Reference Manual

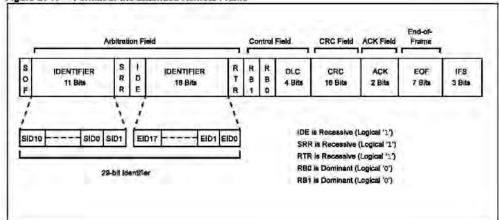

### 21.2 CAN MESSAGE FORMATS

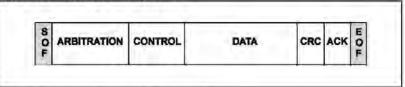

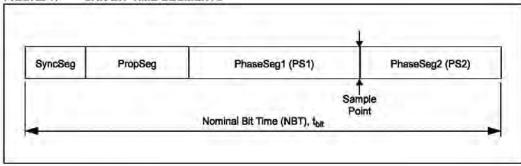

The CAN bus protocol uses asynchronous communication. Information is passed from transmitters to receivers in data frames, which are composed of byte fields that define the contents of the data frame, as shown in Figure 21-3.

Each frame begins with a Start-of-Frame (SOF) bit and terminates with an End-of-Frame (EOF) bit field. The Start-of-Frame is followed by Arbitration and Control fields, which identify the message type, format, length and priority. This information allows each node on the CAN bus to respond appropriately to the message. The Data field conveys the message content and is variable length, ranging from 0 to 8 bytes. Error protection is provided by the Cyclic Redundancy Check (CRC) and Acknowledgement (ACK) fields.

Figure 21-3: CAN Bus Message Frame

The CAN bus protocol supports five frame types:

- · Data Frame carries data from transmitter to the receivers

- Remote Frame transmitted by a node on the bus, to request transmission of a data frame with the same identifier from another node

- · Error Frame transmitted by any node when it detects an error

- Overload Frame provides an extra delay between successive Data or remote frames

- · Interframe Space provides a separation between successive frames

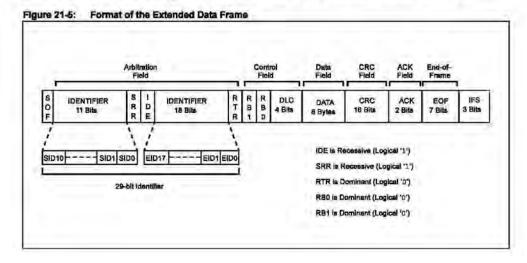

The CAN 2.0B specification defines two additional data formats:

- · Standard Data Frame intended for standard messages that use 11 identifier bits

- Extended Data Frame intended for extended messages that use 29 identifier bits

There are three versions of CAN Bus specifications:

- · 2.0A considers 29-bit identifier as error

- 2.0B Passive ignores 29-bit identifier messages

- 2.0B Active handles both 11-bit and 29-bit identifier

The dsPIC33F ECAN module is compliant with the CAN 2.0B active specification, while providing enhanced message filtering capabilities.

Note: Refer to the Bosch CAN bus specification for detailed information on the CAN protocol.

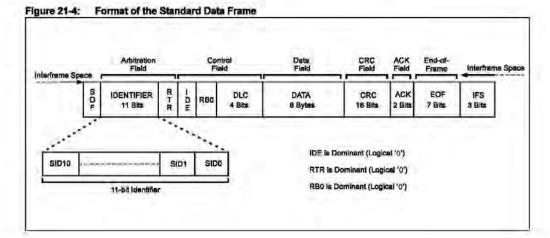

#### 21.2.1 Standard Data Frame

The standard data frame message begins with a Start-of-Frame bit followed by a 12-bit Arbitration field, as shown in Figure 21-4. The Arbitration field contains an 11-bit identifier and the Remote Transmit Request (RTR) bit. The identifier defines the type of information contained in the message and is used by each receiving node to determine if the message is of interest to it. The RTR bit distinguishes a data frame from a remote frame. For a standard data frame, the RTR bit is clear.

Following the Arbitration field is a 6-bit Control field, which provides more information about the contents of the message. The first bit in the Control field is an Identifier Extension (IDE) bit, which distinguishes the message as either a Standard or Extended data frame. A standard data frame is indicated by a dominant state (logic level '0') during transmission of the IDE bit. The second bit in the Control field is a Reserved (RB0) bit, which is in the dominant state (logic level '0'). The last 4 bits in the Control field represent the Data Length Code (DLC), which specifies the number of data bytes present in the message.